| 1<br>2<br>3<br>4<br>5 | David A. Nelson ( <i>pro hac vice</i> forthcoming)<br>(III. Bar No. 6209623)<br>davenelson@quinnemanuel.com<br>QUINN EMANUEL URQUHART & SULLIVAN, LLP<br>500 West Madison St., Suite 2450<br>Chicago, Illinois 60661<br>Telephone: (312) 705-7400<br>Facsimile: (312) 705-7401 |                                      |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 6                     |                                                                                                                                                                                                                                                                                |                                      |

| 7<br>8                | Karen P. Hewitt (SBN 145309)<br>kphewitt@jonesday.com                                                                                                                                                                                                                          |                                      |

| 8<br>9                | Randall E. Kay (SBN 149369)                                                                                                                                                                                                                                                    |                                      |

| 10                    | rekay@jonesday.com<br>JONES DAY                                                                                                                                                                                                                                                |                                      |

| 10                    | 4655 Executive Drive, Suite 1500<br>San Diego, California 92121                                                                                                                                                                                                                |                                      |

| 12                    | Telephone: (858) 314-1200                                                                                                                                                                                                                                                      |                                      |

| 13                    | Facsimile: (858) 345-3178                                                                                                                                                                                                                                                      |                                      |

| 14                    | Evan R. Chesler ( <i>pro hac vice</i> forthcoming)                                                                                                                                                                                                                             |                                      |

| 15                    | (N.Y. Bar No. 1475722)<br>echesler@cravath.com                                                                                                                                                                                                                                 |                                      |

| 16                    | CRAVATH, SWAINE & MOORE LLP                                                                                                                                                                                                                                                    |                                      |

| 17                    | Worldwide Plaza, 825 Eighth Avenue<br>New York, NY 10019                                                                                                                                                                                                                       |                                      |

| 18                    | Telephone: (212) 474-1000                                                                                                                                                                                                                                                      |                                      |

| 19                    | Facsimile: (212) 474-3700                                                                                                                                                                                                                                                      |                                      |

| 20                    | Attorneys for Plaintiff                                                                                                                                                                                                                                                        |                                      |

| 21                    | QUALCOMM INCORPORATED                                                                                                                                                                                                                                                          |                                      |

| 22                    | UNITED STATES DISTRICT COURT                                                                                                                                                                                                                                                   |                                      |

| 23                    | SOUTHERN DISTRICT OF CALIFORNIA                                                                                                                                                                                                                                                |                                      |

| 24                    | QUALCOMM INCORPORATED,                                                                                                                                                                                                                                                         | Case No. <u>'17CV1375 JAH AGS</u>    |

| 25                    | Plaintiff,                                                                                                                                                                                                                                                                     | COMPLAINT FOR PATENT<br>INFRINGEMENT |

| 26                    |                                                                                                                                                                                                                                                                                | [DEMAND FOR A JURY TRIAL]            |

| 27                    | APPLE INCORPORATED,                                                                                                                                                                                                                                                            |                                      |

| 28                    | Defendant.                                                                                                                                                                                                                                                                     |                                      |

|                       | COMPLAINT                                                                                                                                                                                                                                                                      |                                      |

|                       |                                                                                                                                                                                                                                                                                |                                      |

Plaintiff Qualcomm Incorporated ("Qualcomm"), by its undersigned

attorneys, alleges, with knowledge with respect to its own acts and on information

and belief as to other matters, as follows:

4

## NATURE OF THE ACTION

I. Qualcomm brings this action to compel Apple to cease infringing

Qualcomm's patents and to compensate Qualcomm for Apple's extensive

infringement of several patented Qualcomm technologies.

8 2. Qualcomm is one of the world's leading technology companies and a

9 pioneer in the mobile phone industry. Its inventions form the very core of modern

10 mobile communication and enable modern consumer experiences on mobile devices

11 and cellular networks.

3. Since its founding in 1985, Qualcomm has been designing, developing,

and improving mobile communication devices, systems, networks, and products. It

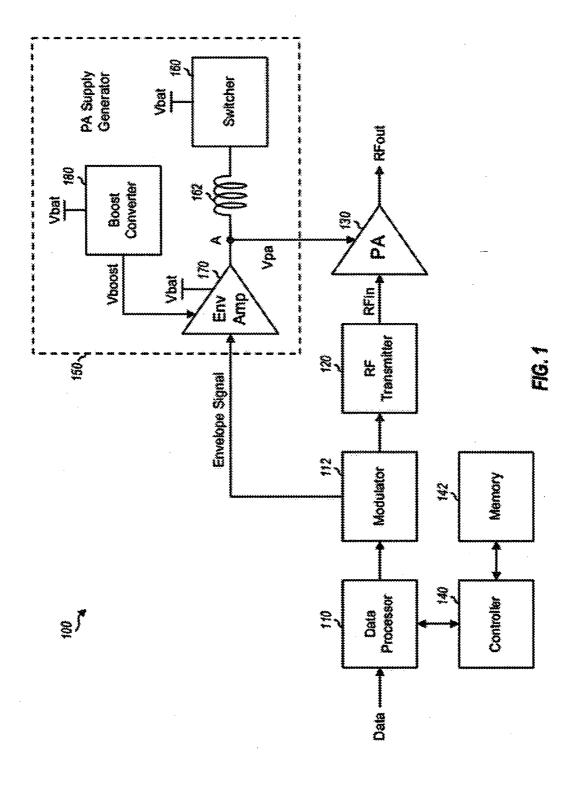

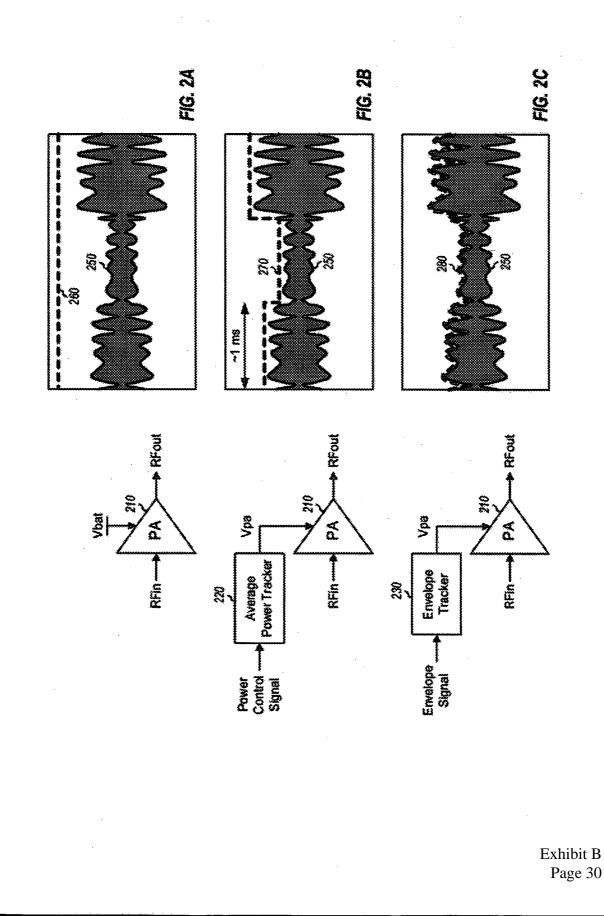

has invented technologies that transform how the world communicates. Qualcomm

developed fundamental technologies at the heart of 2G, 3G, and 4G cellular

communications, is leading the industry to 5G cellular communications, and has

developed numerous innovative features used in virtually every modern cell phone.

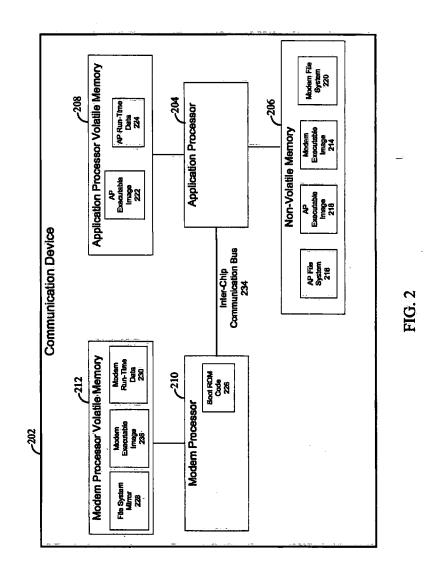

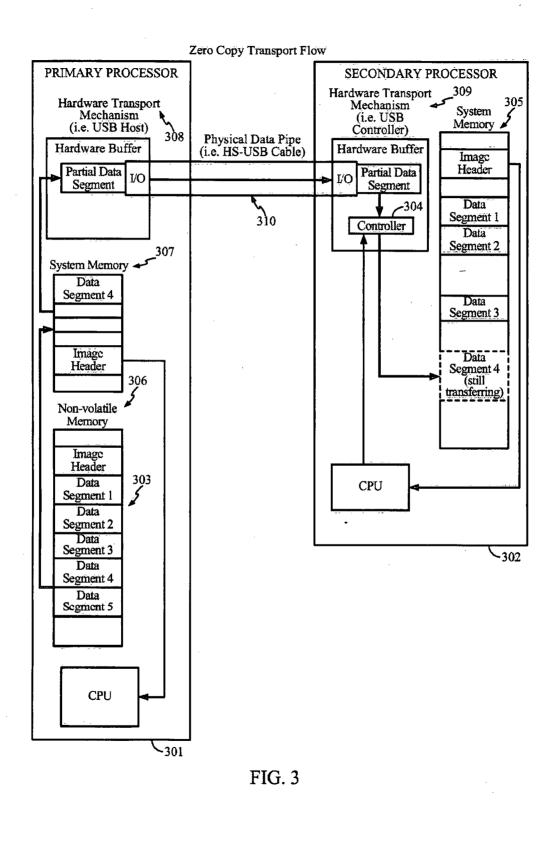

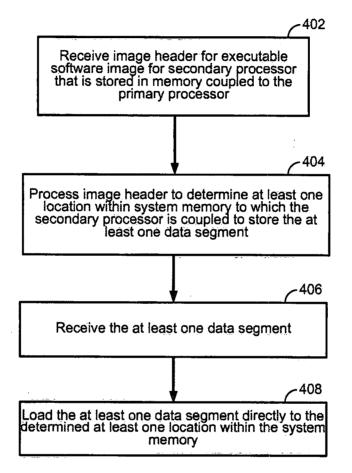

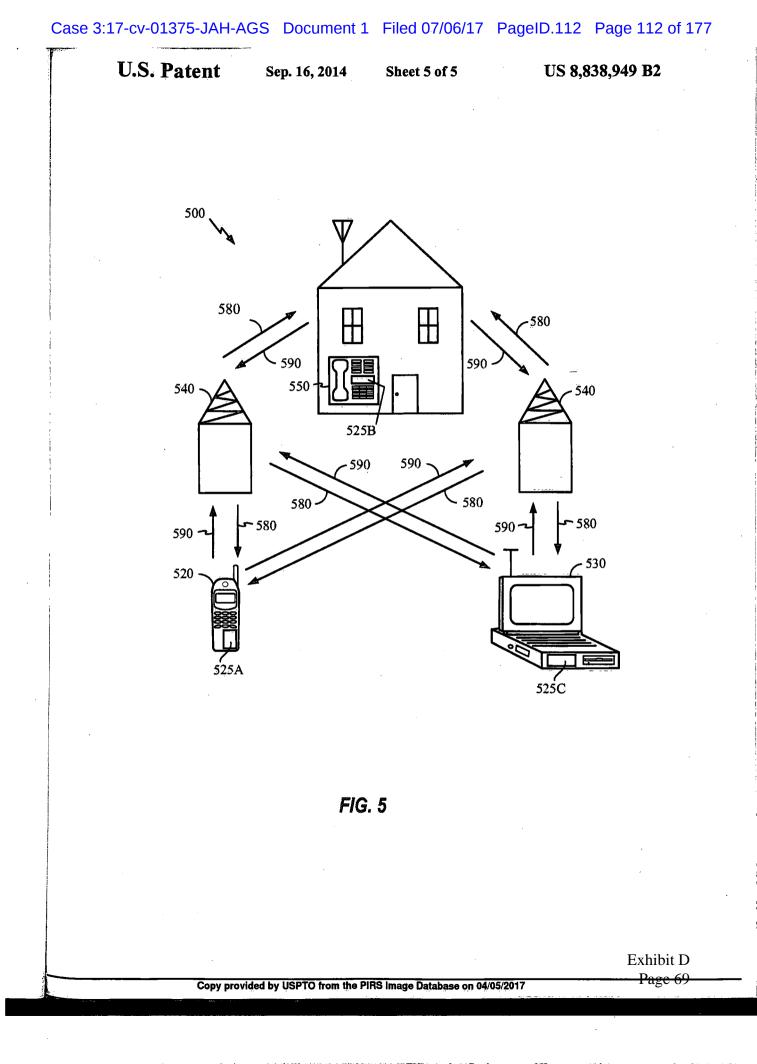

4. Qualcomm also invests in technologies developed by other companies

and has acquired companies (and their patented innovative technologies) as part of

its emphasis on supporting innovation. Qualcomm's patent portfolio currently

includes more than 130,000 issued patents and patent applications worldwide.

Hundreds of mobile device suppliers around the world have taken licenses from

Qualcomm.

5. Apple is the world's most profitable seller of mobile devices. Its

iPhones and other products enjoy enormous commercial success. But without the

innovative technology covered by Qualcomm's patent portfolio, Apple's products

would lose much of their consumer appeal. Apple was a relatively late entrant in the

mobile device industry and its mobile devices rely heavily on the inventions of

COMPLAINT

-2-

Qualcomm and other companies that Qualcomm has invested in. Nearly a decade 1 2 before Apple released the iPhone, Qualcomm unveiled its own full-feature, top-of-3 the-line smartphone. According to CNN's 1999 holiday buying guide, Qualcomm's pdQ 1900 "lets you make calls, keep records, send email, browse the web and run 4 5 over a thousand different applications, all while on the go. Although a cell phone, it is one of the first truly portable, mobile and multipurpose Internet devices."<sup>1</sup> While 6 7 Qualcomm no longer markets phones directly to consumers, it continues to lead the 8 development of cutting-edge technologies that underpin a wide range of important 9 wireless-device features. Other companies, like Apple, now manufacture and market phones that feature Qualcomm's innovations and the innovations of other 10 11 technology pioneers that Qualcomm invested in.

12 Qualcomm's innovations in the mobile space have influenced all 6. 13 modern smartphones, and Apple-like other major mobile device makers-utilizes 14 Qualcomm's technologies. Qualcomm's patented features enable and enhance popular features that drive consumer demand, for example, enhancements to high 15 16 performance and power efficient graphics processing architectures, reducing power 17 consumption and increasing battery life through envelope tracking, reducing power 18 consumption and increasing efficiency of integrated circuits through voltage level 19 shifter improvements, "flashless boot" technology that reduces memory expenses 20 with little to no performance impact, reducing circuit power consumption by 21 minimizing power-intensive bus activation, and power-efficient carrier aggregation 22 allowing faster network performance and longer battery life, among many others.

- 7. In short, Qualcomm invented many core technologies that make the

iPhone (and other smartphones and mobile devices) desirable to consumers in their

daily lives.

- 26

- 27

- 28

http://edition.cnn.com/1999/TECH/ptech/12/03/qualcomm.pdq/

1 8. While Apple built the most successful consumer products in history by 2 relying significantly on technologies pioneered by Qualcomm, Apple refuses to pay 3 for those technologies. Apple's founder boasted that Apple "steals" the great ideas of others-specifically, that "we have always been shameless about stealing great 4 ideas."<sup>2</sup> Apple employees likewise admit that Apple—a relatively late entrant in the 5 mobile space-did not invent many of the iPhone's features. Instead, Apple 6 7 incorporated, marketed, and commercialized the work of others: "I don't know how 8 many things we can come up with that you could legitimately claim we did first.... 9 We had the first commercially successful version of many features but that's different than launching something to market first."<sup>3</sup> 10

11 9. Rather than pay Qualcomm for the technology Apple uses, Apple has taken extraordinary measures to avoid paying Qualcomm for the fair value of 12 13 Qualcomm's patents. On January 20, 2017, Apple sued Qualcomm in this district, 14 asserting an array of excuses to avoid paying fair-market, industry-standard rates for 15 the use of certain of Qualcomm's pioneering patents that are critical to a modern 16 smartphone like the iPhone. See Case No. 3:17-cv-00108-GPC-MDD. Apple also 17 encouraged the companies that manufacture the iPhone to breach their contracts 18 with Qualcomm by refusing to pay for the Qualcomm technology in iPhones, 19 something that those manufacturers had done for many years, without complaint, 20 before Apple's direction to stop. Further, Apple misled governmental agencies around the world into investigating Qualcomm in an effort to indirectly exert 21

22

Interview with Steve Jobs, available at

https://www.youtube.com/watch?v=CW0DUg63lqU ("Picasso had a saying, 'good artists copy, great artists steal.' And we have always been shameless about stealing great ideas.").

<sup>27</sup> Embedded (Aug. 3, 2012), <u>http://www.embedded.com/print/4391702</u> (April 21,

$_{28}$  2017 snapshot of page, accessed via Google's cache).

<sup>&</sup>lt;sup>26</sup> April 2010 email from Apple's iPhone Product Marketing Manager, Steve Sinclair, reported in: Rick Merritt, *Schiller 'shocked at 'copycat' Samsung phone*,

1 leverage over Qualcomm.

Many of Qualcomm's patents are essential to certain cellular or other 2 10. 3 standards ("Standard Essential Patents," or "SEPs"), such that the use of an 4 underlying technological standard would require use of the patent. Qualcomm owns 5 a wide range of non-standard-essential patents for inventions in various technologies related to mobile devices. 6

7 11. In this suit, Qualcomm asserts a set of six non-standard-essential 8 patents infringed by Apple's mobile electronic devices. The patents asserted in this 9 suit represent only a small fraction of the Qualcomm non-standard-essential patents 10 that Apple uses without a license.

11 Qualcomm repeatedly offered to license its patents to Apple. But 12. Apple has repeatedly refused offers to license Qualcomm's patents on reasonable 12 13 terms. Qualcomm therefore seeks to enforce its rights in the patents identified below and to address and remedy Apple's flagrant infringement of those patents. 14 15

PARTIES

16 13. Qualcomm is a Delaware corporation with its principal place of business at 5775 Morehouse Drive, San Diego, California. Since 1989, when 17 18 Qualcomm publicly introduced Code Division Multiple Access ("CDMA") as a 19 commercially successful digital cellular communications standard, Qualcomm has 20 been recognized as an industry leader and innovator in the field of mobile devices 21 and cellular communications. Qualcomm owns more than 130,000 patents and 22 patent applications around the world relating to cellular technologies and many 23 other valuable technologies used by mobile devices. Qualcomm is a leader in the 24 development and commercialization of wireless technologies and the owner of the 25 world's most significant portfolio of cellular technology patents. Qualcomm derives 26 a substantial portion of its revenues and profits from licensing its intellectual 27 property. Qualcomm is also a world leader in the sale of chips, chipsets, and 28 associated software for mobile phones and other wireless devices.

COMPLAINT

-5-

1 14. Apple is a corporation organized and existing under the laws of the 2 State of California, with its principal place of business at 1 Infinite Loop, Cupertino, 3 California. Apple designs, manufactures, and sells throughout the world a wide range of products, including mobile devices that incorporate Qualcomm's patented 4 5 technologies.

6

21

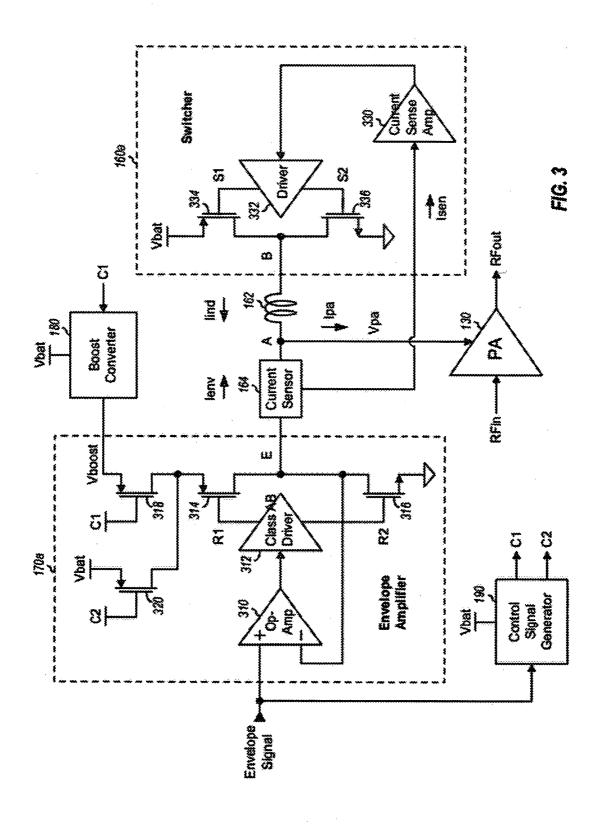

24

# JURISDICTION AND VENUE

7 15. This action arises under the patent laws of the United States of 8 America, 35 U.S.C. § 1 et seq. This Court has jurisdiction over the subject matter of 9 this action pursuant to 28 U.S.C. §§ 1331 and 1338(a).

10 16. This Court has personal jurisdiction over Apple because it is organized 11 and exists under the laws of California.

12 Venue is proper in this District pursuant to 28 U.S.C. § 1391(b) and (c) 17. 13 and 28 U.S.C. § 1400(b). Venue is appropriate under 28 U.S.C. 1400(b) at least 14 because Apple is incorporated in California and because Apple has committed acts 15 of infringement and has a regular and established place of business in this district. 16 Apple's acts of infringement in this district include but are not limited to sales of the 17 Accused Products at Apple Store locations in this district, including but not limited 18 to 7007 Friars Road, San Diego, CA 92108 and 4505 La Jolla Village Drive, San 19 Diego, CA 92122.

20 STATEMENT OF FACTS **Qualcomm Background** 22 18. Qualcomm was founded in 1985 when seven industry visionaries came 23 together to discuss the idea of providing quality communications. For more than 30 years, Qualcomm has been in the business of researching, designing, developing,

25 and selling innovative semiconductor and cellular technology and products for the telecommunications and mobile technology industries. 26

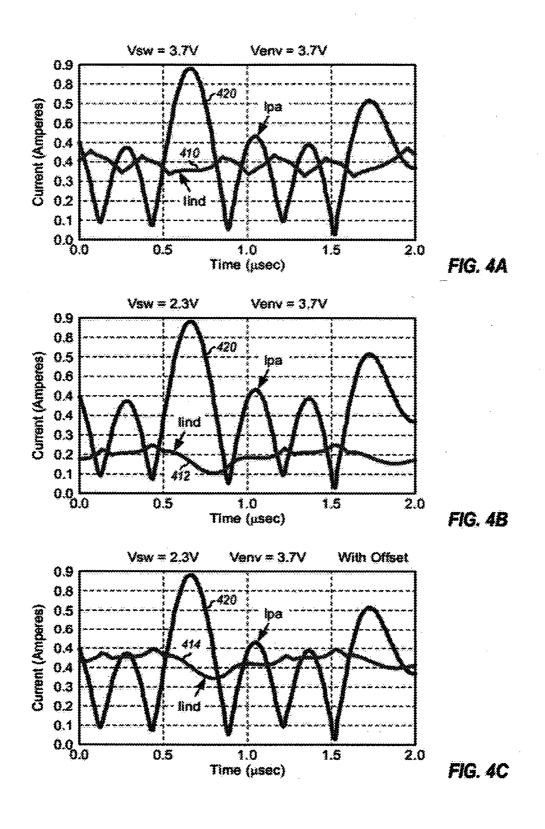

27 19. When Qualcomm was founded, cellular phones were cumbersome, 28 heavy and expensive devices that supplied inconsistent voice communications-

audio quality was poor, users sometimes heard portions of others calls, handoffs

were noisy, and calls frequently dropped. Qualcomm played a central role in the

revolutionary transformation of cellular communications technologies. Today,

cellular devices are remarkably powerful and can deliver reliable voice service and

lightning-fast data to billions of consumers around the world at affordable prices.

20. Qualcomm is now one of the largest technology, semiconductor, and

telecommunications companies in the United States. It employs over 18,000 people

in the United States, 68 percent of whom are engineers, and it occupies more than

92 buildings (totaling over 6.5 million sq. ft.) in seventeen states and the District of

Columbia.

11 Qualcomm's industry-leading research and development efforts, 21. 12 focused on enabling cellular systems and products, are at the core of Qualcomm's 13 business. Since its founding, Qualcomm has invested tens of billions of dollars in 14 research and development related to cellular, wireless communications, and mobile 15 processor technology. Qualcomm's massive research and development investments 16 have produced numerous innovations. Because of this ongoing investment, 17 Qualcomm continues to drive the development and commercialization of successive 18 generations of mobile technology and is one of a handful of companies leading the 19 development of the next-generation 5G standard.

20 22. In addition to Qualcomm's investments in research and development

21 internally, Qualcomm has a rich history of investing in and acquiring technologies

22 developed by other industry leaders. By purchasing companies and patents from

23 companies who desire to sell their innovations, Qualcomm fosters innovation by

24 enabling those companies to realize a return on their research and development

25 investments and, therefore, incentivizes additional research and development.

26 23. As a result of the strength and value of Qualcomm's patent portfolio,

27 virtually every major handset manufacturer in the world has taken a royalty-bearing

28 license to Qualcomm's patent portfolio. The licenses to Qualcomm's patents allow

manufacturers to use numerous forms of critical and innovative Qualcomm

technology without having to bear the multi-billion dollar, multi-year costs of

developing those innovations themselves.

4

### **Apple Background**

5 Apple has built the most profitable company in the world, thanks in 24. 6 large part to products that rely on Qualcomm's patented technologies. With a 7 market capitalization of more than \$700 billion, \$246 billion in cash reserves, and a 8 global sphere of influence, Apple has more money and more influence than many 9 countries. Relying heavily on Qualcomm technology and technology Qualcomm 10 has acquired, Apple has become the dominant player in mobile device sales. 11 Apple's dominance has grown every year since the iPhone's launch in 2007. In 12 recent years, Apple has captured upwards of 90 percent of all profits in the 13 smartphone industry.

14

### Qualcomm's Technology Leadership

15 25. The asserted patents reflect the breadth of Qualcomm's dedication and

16 investment in research and development relating to wireless technology. Qualcomm

17 invented numerous proprietary solutions that are used to optimize products around

18 the globe. Many of those inventions are reflected in Qualcomm's non-standard19 essential patents (such as the patents asserted in this case).

2026. As mobile electronic devices have become more powerful with greater 21 functionality, device manufacturers have faced numerous problems with power 22 consumption, noise reduction, battery charging, graphics processing and heat 23 dissipation, among others. The asserted patents disclose and claim Qualcomm 24 technology that solves many of these problems by enhancing chip performance 25 through advanced carrier aggregation, power-efficient envelope tracking, power-26 efficient boot up and inter-chip communication techniques, area- and power-27 efficient circuit designs, and more powerful and efficient graphics processing 28 circuitry and techniques.

COMPLAINT

-8-

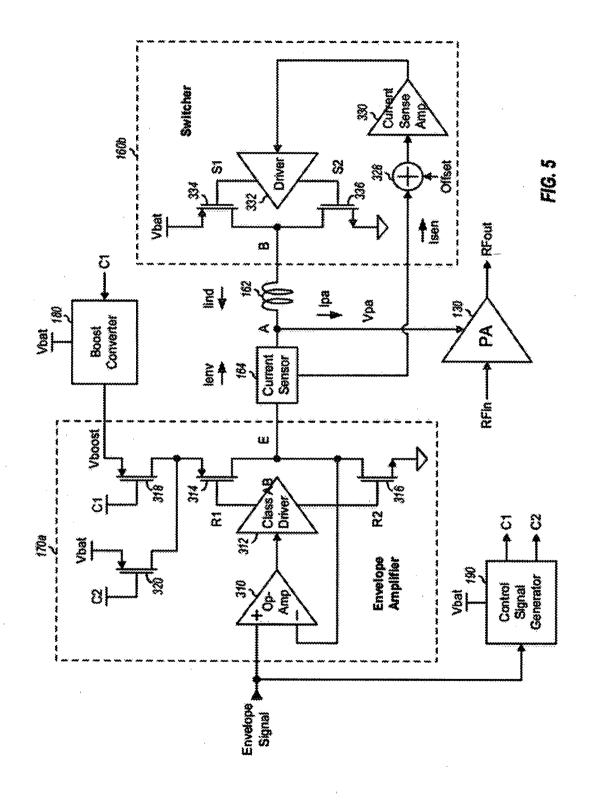

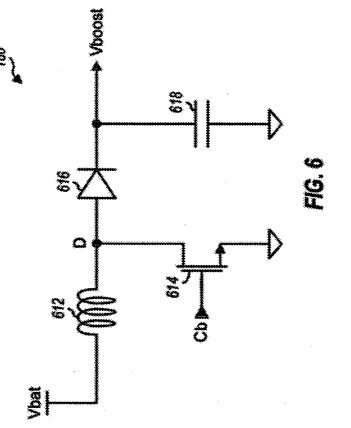

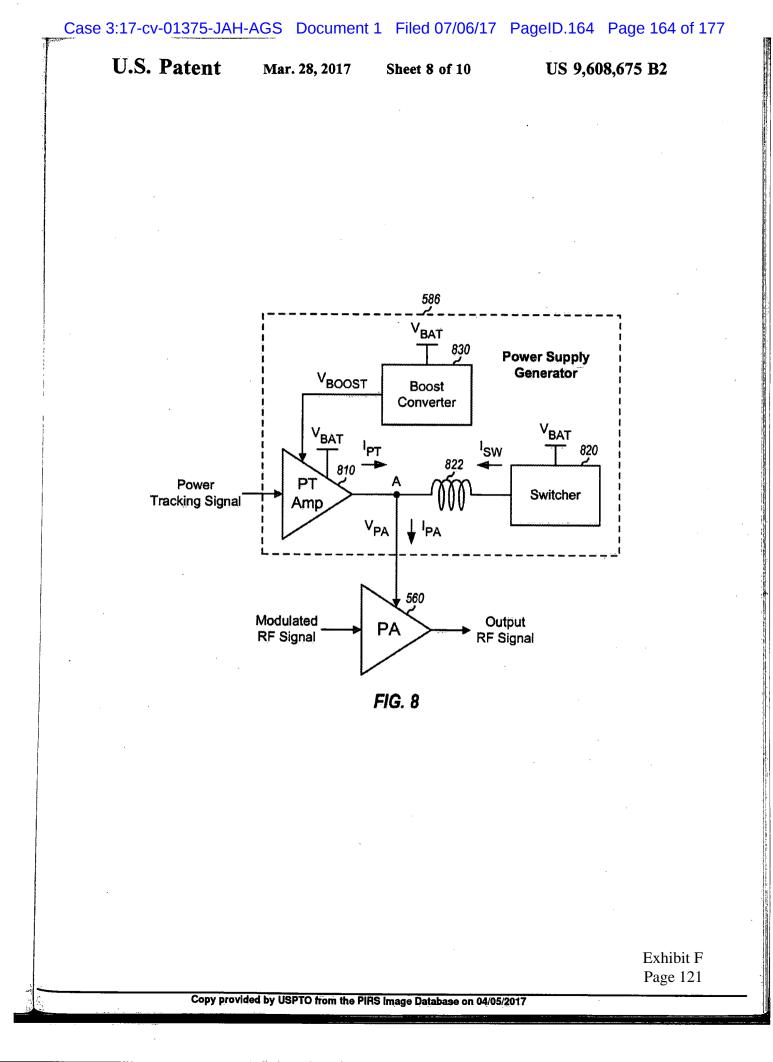

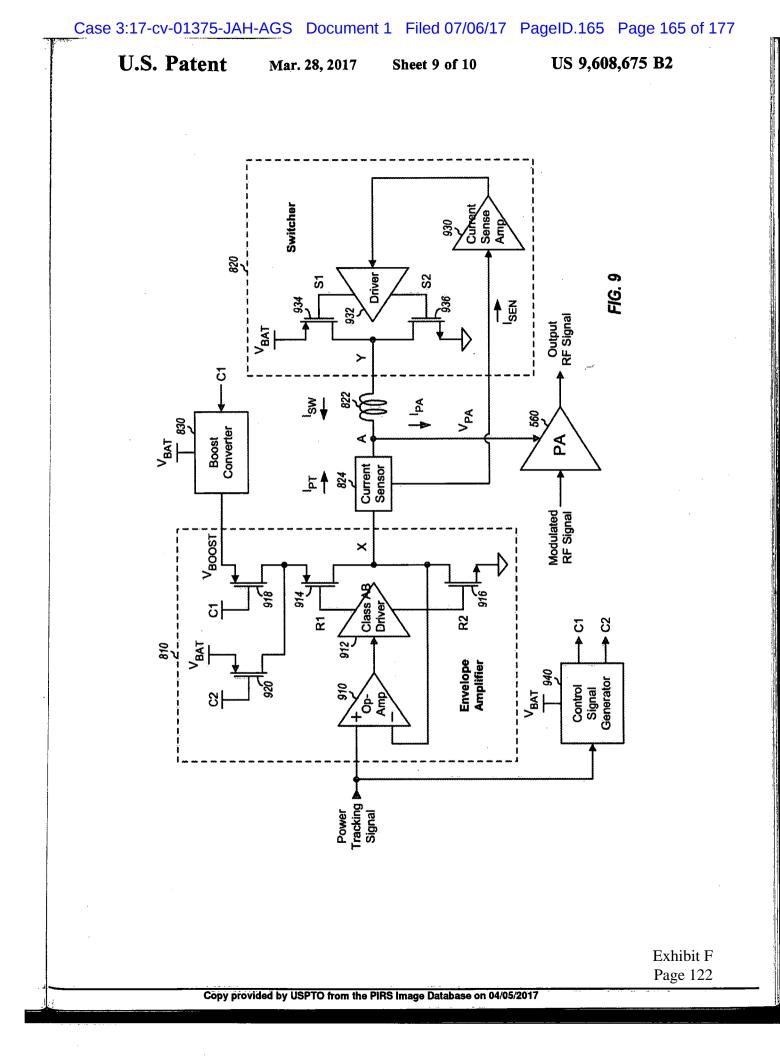

For example, Qualcomm pioneered various "envelope tracking" 1 27. 2 techniques for mobile devices to save power and reduce heat inside a mobile device 3 when transmitting at different signal strength. Using one of these techniques as set 4 forth in Qualcomm's '558 patent, the radio frequency (RF) amplifier power supply 5 is continuously adjusted and dynamically boosted, as necessary, to ensure that the amplifier is operating at peak efficiency for the power required during transmission. 6 7 Envelope tracking allows for a thinner, lighter mobile electronic device that 8 generates less heat. Without envelope tracking, power is wasted and battery life is 9 shorter.

10 28. As another example, Apple has touted the capability of its newest mobile electronic devices to support "carrier aggregation" technology. This means 11 12 that a mobile device can simultaneously transmit radio signals for multiple carriers, 13 which again allows for a more efficient use of power and longer battery life. 14 Indeed, Apple's Senior Vice President of Worldwide Marketing proclaimed that one of the differentiating features of the iPhone 6 is that its enhanced speed is done 15 "with a technology called carrier aggregation."<sup>4</sup> Qualcomm has pioneered and 16 patented technologies that allow this carrier aggregation to be utilized more 17 18 efficiently and with less wasted power.

29. Qualcomm has also pioneered breakthrough mobile graphics

technologies. Each of Qualcomm's industry-leading Snapdragon processors employ

advanced Adreno series graphics processing units ("GPUs"). Mobile device GPUs

must be powerful enough to meet the increasing computational demands of mobile

operating systems without unnecessarily draining the battery life of the mobile

device. The Adreno GPU architecture is the "highest-performance GPU ever

- 25

- 26

<sup>&</sup>lt;sup>4</sup> <u>https://singjupost.com/apple-iphone-6-keynote-september-2014-launch-event-</u>

<u>full-transcript/?singlepage=1</u> (emphasis added).

designed by Qualcomm," providing 40% lower power consumption with 40% faster

performance than the previous Adreno series.<sup>5</sup>

3 30. Qualcomm's patented graphics processing architecture delivers efficiency gains while simultaneously providing excellent performance-receiving 4 praise from Forbes for "dazzl[ing] in GPU performance."<sup>6</sup> Apple heavily markets 5 its GPU performance, claiming that the GPU in the iPhone 7 would "deliver 50% 6 more graphics performance than the [the previous version]."<sup>7</sup> Apple has chosen to 7 8 use Qualcomm's patented improvements to graphics processing architecture, 9 including U.S. Patent No. 8,633,936, without paying for them, to deliver high speed 10 and power-efficient graphics that Apple promises and its customers now demand.

11 31. Qualcomm has invested substantially in both advancing standards and the quality of service provided to anyone using that standard, as well as proprietary 12 13 implementations of modem technology (e.g., innovations in lowering costs and 14 driving efficiency). For example, Qualcomm is a pioneer in "flashless boot" 15 technology, to which the '949 patent relates, which enables phone manufacturers to 16 use less storage in relation to wireless modems. Storage in a handheld device can be 17 both expensive and contribute to weight and size concerns. Indeed, incremental increases in flash storage for currently available iPhones can cost \$100,<sup>8</sup> and Apple 18 19 has also touted its iPhone devices as thin and light.

32. Similarly, Qualcomm has invested and developed novel solutions to

save power in mobile devices, including by synchronizing messages within a mobile

- 22

- <sup>5</sup> <u>https://www.theinquirer.net/inquirer/news/2421804/qualcomm-outs-next-gen-adreno-gpu-ahead-of-snapdragon-820-launch.</u>

- 25 https://www.forbes.com/sites/moorinsights/2017/03/23/qualcomms-newsnapdragon-835-dazzles-in-gpu-performance/#6b7099262075.

- <sup>7</sup> <u>https://www.extremetech.com/computing/235140-apples-new-a10-fusion-</u>

quad-core-high-efficiency-and-a-more-powerful-gpu.

- 28 https://www.apple.com/shop/buy-iphone/iphone-7.

device to reduce both time and power needed for inter-processor communication.

The '490 patent allows mobile devices to operate just as efficiently with lower

power consumption, which in turn prolongs the battery life of those devices. Apple

benefits from this technology, simultaneously touting the long battery life of its

devices while relying upon a relatively small battery as compared to the iPhone's

peers.

7 33. As a final example, Qualcomm's development of power efficient 8 innovations is unmatched. Qualcomm has invented circuit-level solutions that allow 9 devices to reduce the overall operating voltages of the integrated circuits within the 10 phone, thereby reducing power consumption and increasing efficiency of the 11 integrated circuit. A particularly important circuit in Apple devices is therefore one 12 of the inventions in Qualcomm's '658 patent, relating to a voltage level shifter. 13 Qualcomm's solution significantly reduces the size of level shifting circuits. The 14 compact design claimed in the '658 patent allows Apple to fit more circuits into a 15 layout, thereby saving costs through smaller die sizes and reduced power 16 consumption, which has all the benefits that Apple regularly touts. **The Accused Devices** 17 18 34. As set forth below, a variety of Apple's devices—including certain of 19 Apple's iPhones and iPads —practice one or more of the Patents-in-Suit. 20 **The Patents-in-Suit** 21 35. The following patents are infringed by Apple ("Patents-in-Suit"): U.S. 22 Patent No. 8,633,936 ("the '936 patent"), U.S. Patent No. 8,698,558 ("the '558 23 patent"), U.S. Patent No. 8,487,658 ("the '658 patent"), U.S. Patent No. 8,838,949 24 ("the '949 patent"), U.S. Patent No. 9,535,490 ("the '490 patent"), and U.S. Patent 25 No. 9,608,675 ("the '675 patent"). 26 36. As described below, Apple has been and is still infringing, contributing 27 to infringement, and/or inducing others to infringe the Patents-in-Suit by making, 28 using, offering for sale, selling, or importing devices that practice the Patents-in-

Suit. Apple's acts of infringement have occurred within this District and elsewhere

throughout the United States.

3

### U.S. Patent No. 8,633,936

37. The '936 patent was duly and legally issued on January 21, 2014 to

Qualcomm, which is the owner of the '936 patent and has the full and exclusive

right to bring actions and recover damages for Apple's infringement of the '936

patent. The '936 patent is valid and enforceable. A copy of the '936 Patent is

attached hereto as Exhibit A.

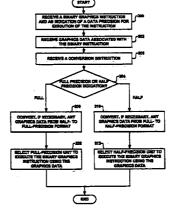

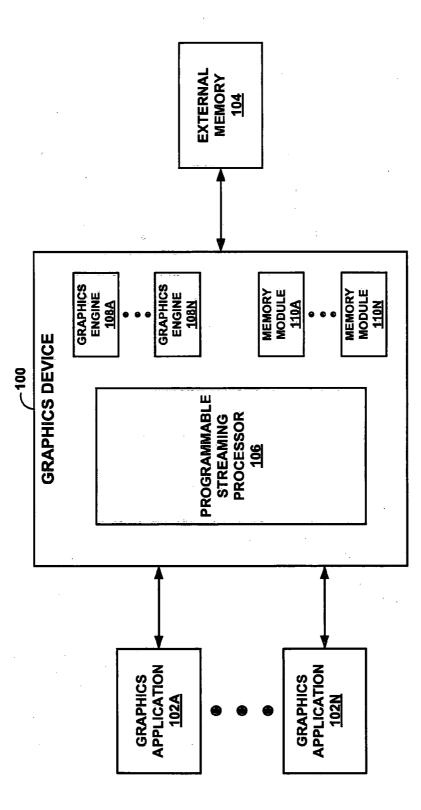

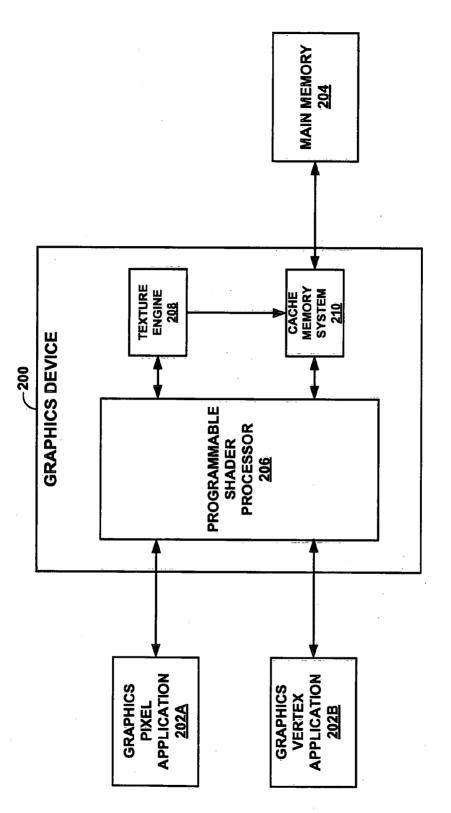

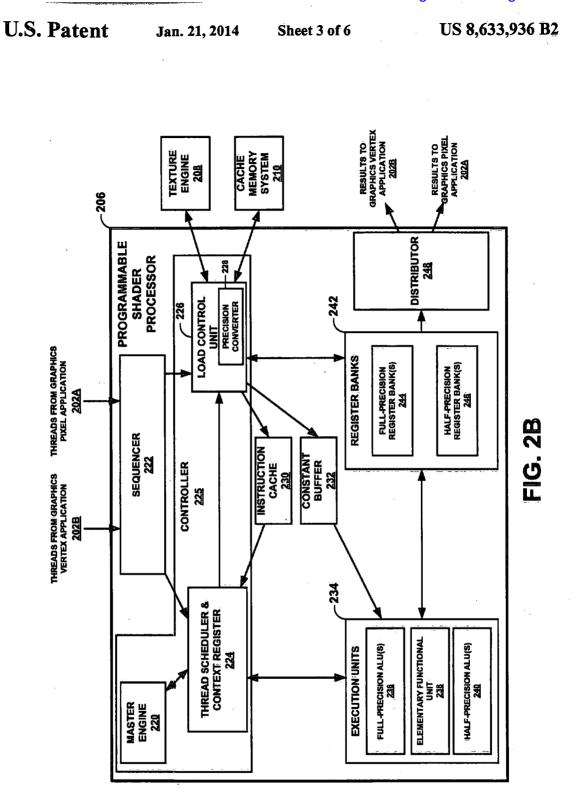

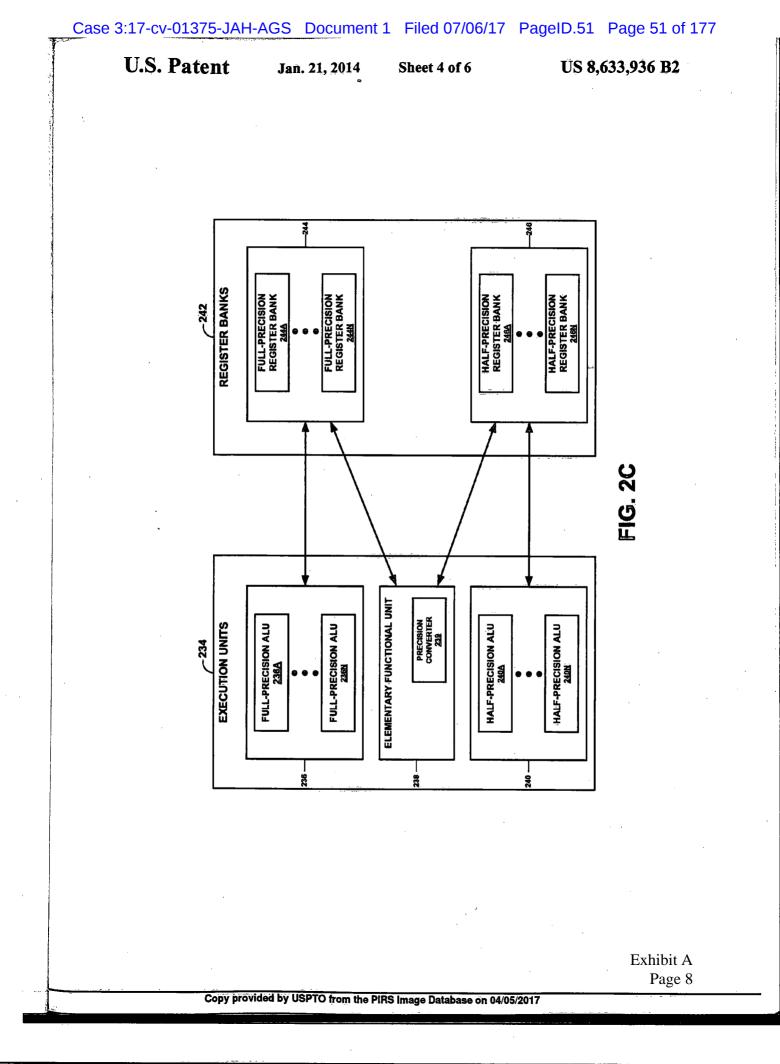

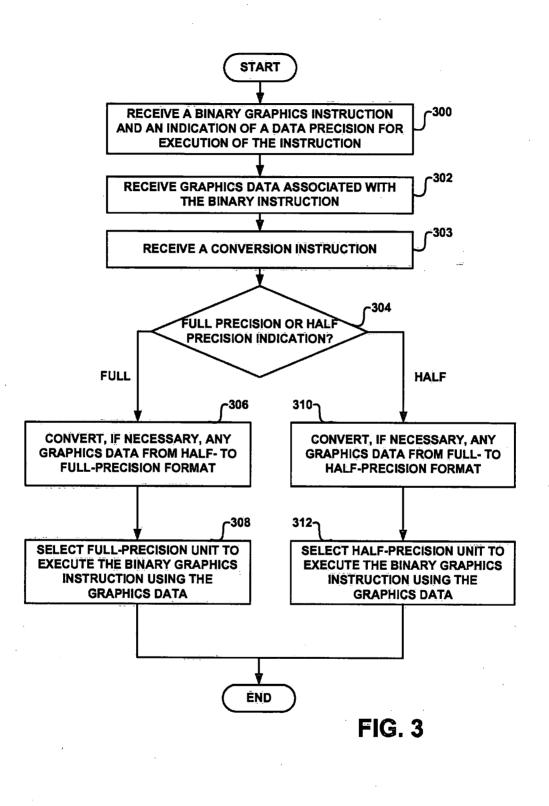

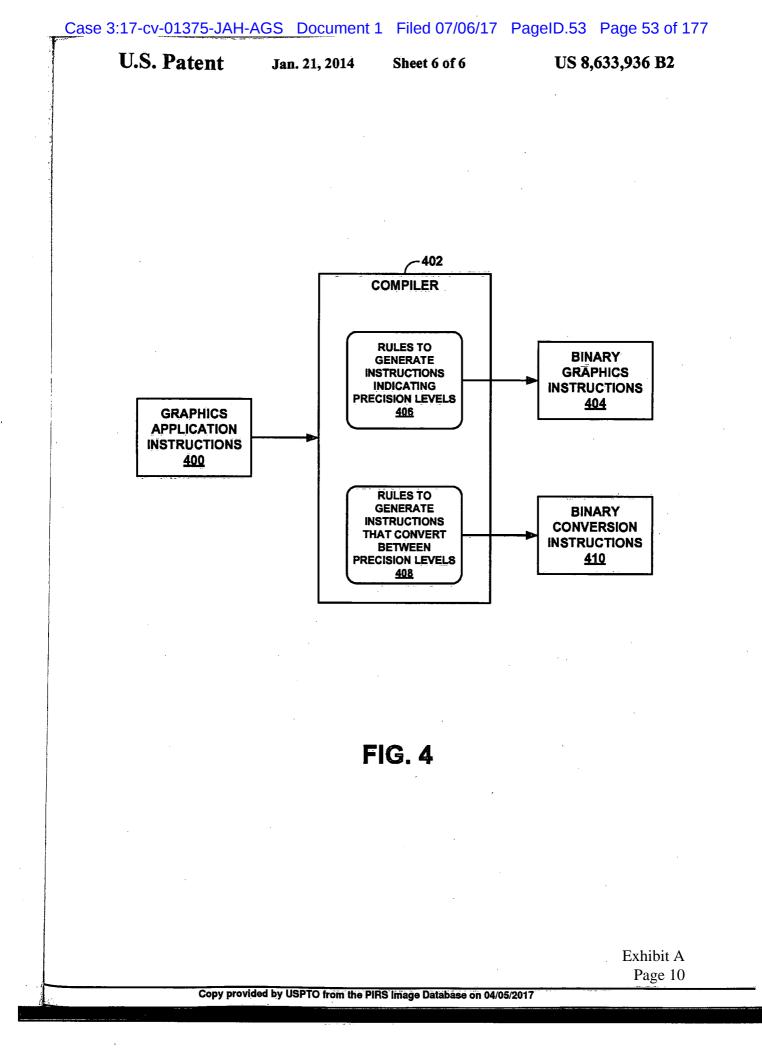

9 38. The '936 patent relates generally to a graphics processing architecture. 10 The '936 patent discloses novel methods and structures for forming graphics 11 processing circuitry incorporating multiple execution units for processing graphics 12 instructions at different graphics precision levels, and for converting graphics data to 13 the correct precision level prior to processing the associated graphics instruction. 14 As a result of the invention of the '936 patent, graphics processors are able to use 15 lower precision execution units, processing graphics data in a higher performance 16 and more power efficient manner, thereby extending battery life.

17

### U.S. Patent No. 8,698,558

39. The '558 patent was duly and legally issued on April 15, 2014, and

Qualcomm is the current owner of the '558 patent and has the full and exclusive

right to bring action and recover damages for Apple's infringement of the '558

patent. The '558 patent is valid and enforceable. A copy of the '558 Patent is

attached hereto as Exhibit B.

40. The '558 patent relates generally to envelope tracking technology,

which addresses the efficient use of power by a power amplifier in transmitting an

output radio frequency (RF) signal. In particular, the power amplifier may require

varying degrees of power supply voltage depending on the type of RF signal being

transmitted. In the past, the use of a constant power supply voltage did not match

the varying power requirements of the power amplifier, and led to unnecessary

dissipation of power (and devices that, due to this unnecessary power dissipation,

quickly drained the battery). Envelope tracking adjusts the power supply voltage

based on information from the modem to match the needs of the power amplifier.

The '558 patent discloses novel circuitry for efficiently and effectively boosting

power supply voltage to continuously match the peak efficiency necessary over the

RF envelope. As a result of the invention of the '558 patent, electronic devices are

able to reduce power consumption and extend battery life.

8

### U.S. Patent No. 8,487,658

9 41. The '658 patent was duly and legally issued on July 16, 2013 to

10 Qualcomm, which is the owner of the '658 patent and has the full and exclusive

11 right to bring action and recover damages for Apple's infringement of the '658

12 patent. The '658 patent is valid and enforceable. A copy of the '658 Patent is

13 attached hereto as Exhibit C.

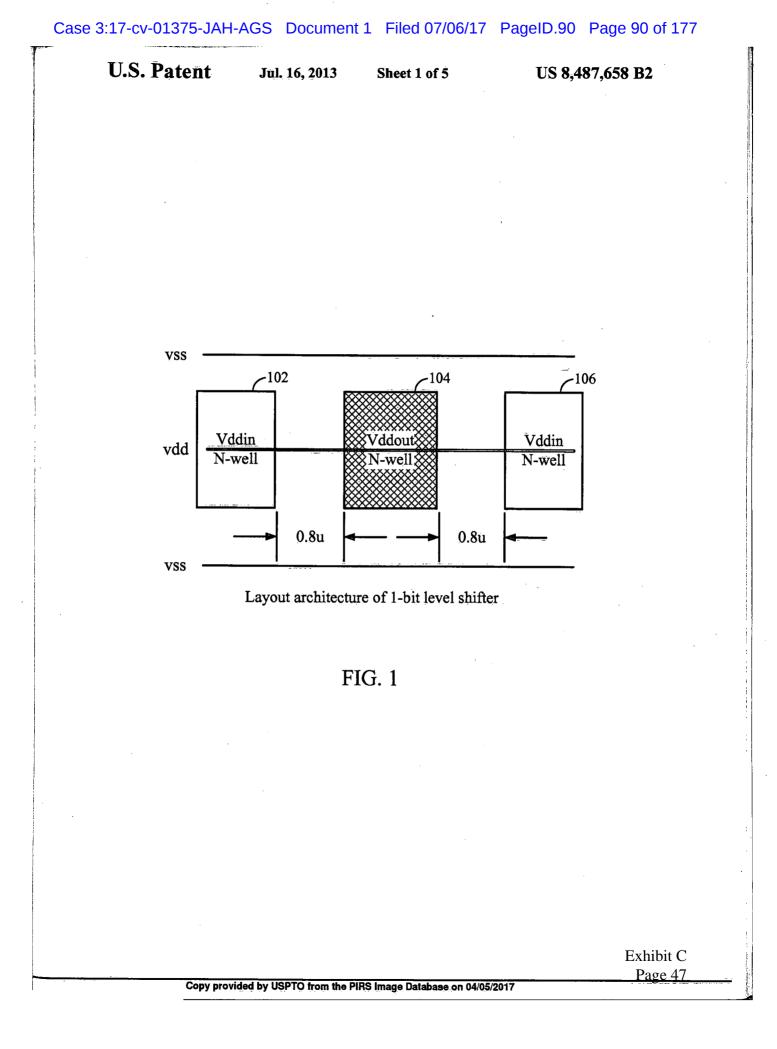

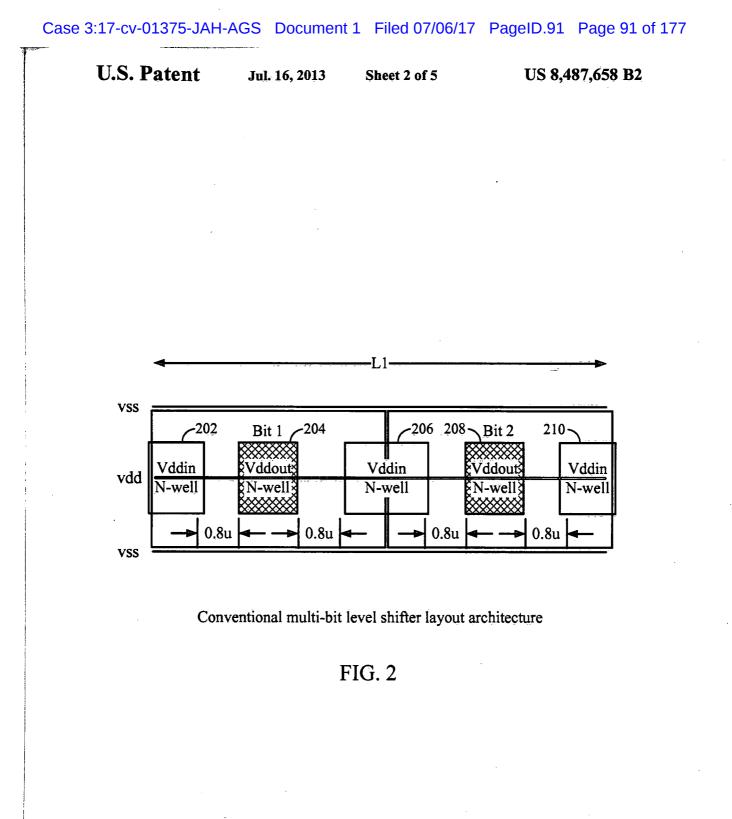

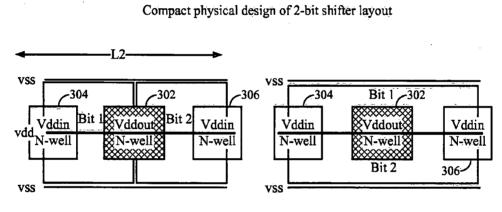

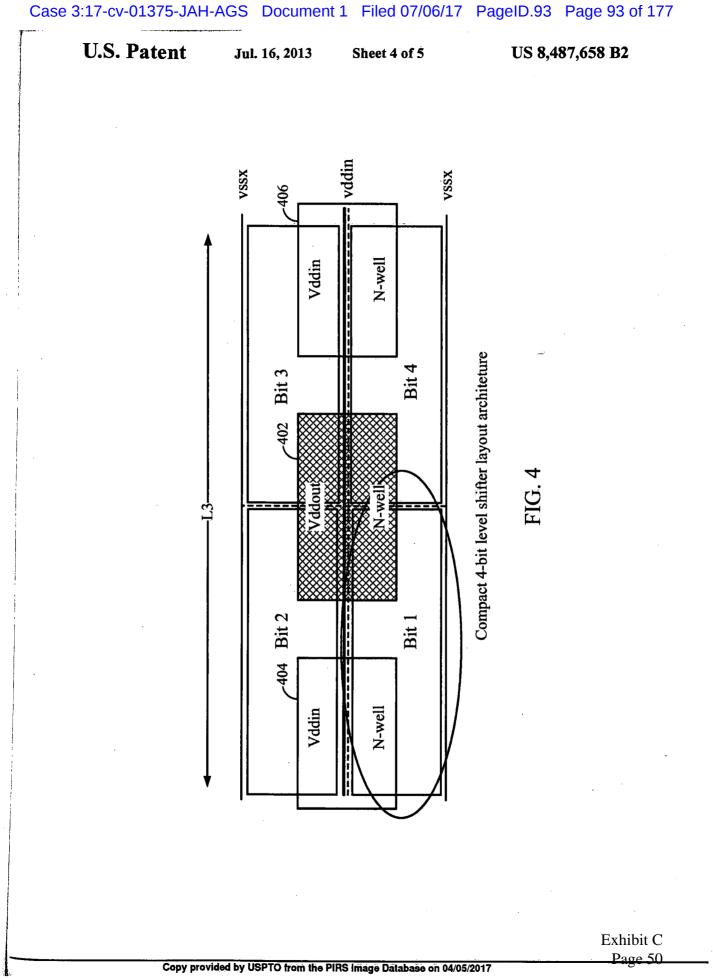

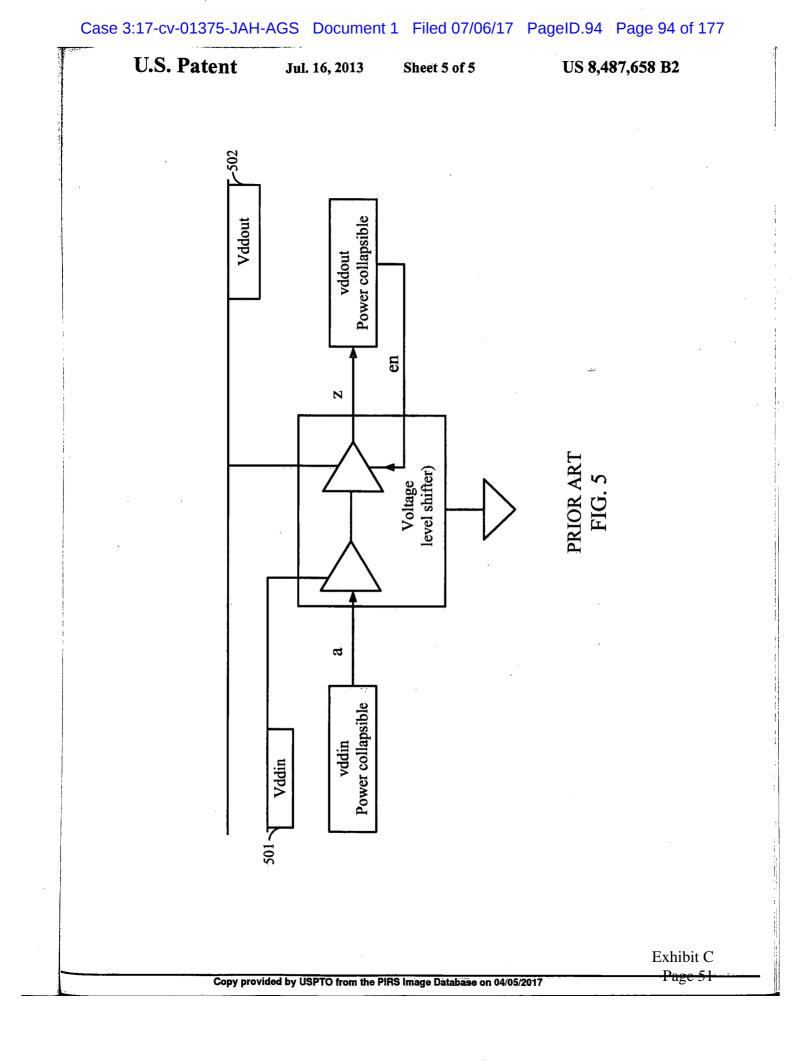

14 42. The '658 patent relates generally to voltage level shifter circuitry. 15 Integrated circuit devices incorporating different types of functional circuitry are 16 often required to handle multiple voltage levels. These devices typically contain a 17 high-voltage circuit driven by a relatively high voltage power supply and a low-18 voltage circuit driven by a relatively low-voltage power supply. Reducing the 19 overall operating voltages of the integrated circuit reduces power consumption and 20 increases efficiency of the integrated circuit. However, some circuits are more 21 amenable to lower operating voltages while others must operate at a higher voltage. 22 For circuits operating at two different voltages to communicate with each other, a 23 level shifter circuit is required as an interface to shift the signal from one voltage 24 level to another to avoid circuit dysfunction. However, because the level shifter 25 itself operates with two different voltages, it is required to have at least two N-wells, 26 one for each voltage. In addition, constraints placed on the N-wells may require them to be separated by a minimum distance. Therefore, incorporating multiple 27 28 level shifters into a single chip can consume a significant portion of the available

COMPLAINT

-13-

chip area. The '658 patent is directed to a compact and robust multi-bit voltage

level shifter design and layout, which may reduce the area of the level shifters.

3

## U.S. Patent No. 8,838,949

4 43. The '949 patent was duly and legally issued on September 16, 2014 to

5 Qualcomm, which is the owner of the '949 patent and has the full and exclusive

6 right to bring actions and recover damages for Apple's infringement of the '949

7 patent. The '949 patent is valid and enforceable. A copy of the '949 Patent is

8 attached hereto as Exhibit D.

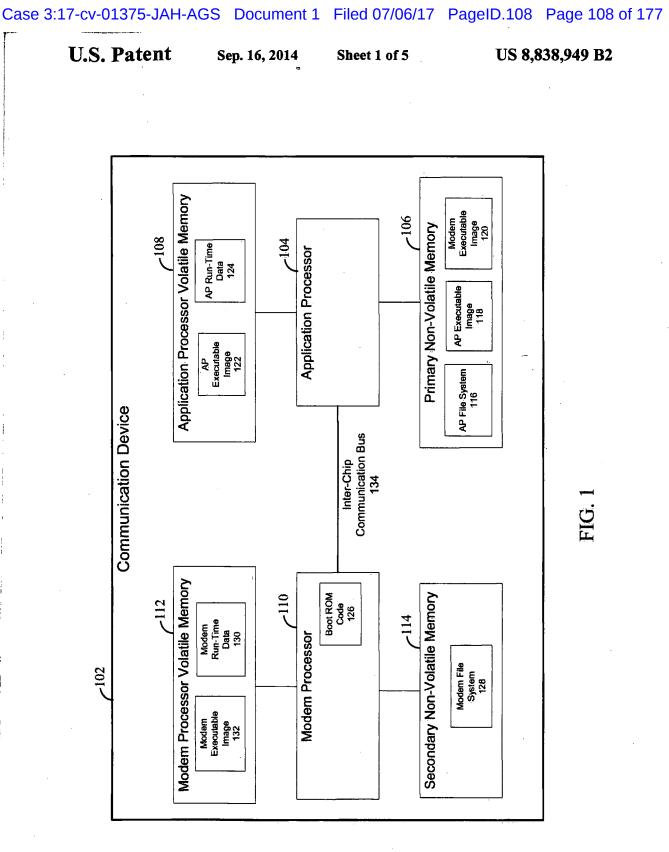

9 44. The '949 patent relates generally to "flashless boot," *i.e.*, booting up a 10 secondary processor that does not have its own non-volatile memory to store the 11 system image. The '949 patent discloses novel techniques for implementing 12 flashless boot for secondary processors in multi-processor systems by using a scatter 13 loader to directly transfer the image into memory of the secondary processor. As a 14 result of the invention of the '949 patent, multi-processor systems-which 15 encompass a device including at least an application processor and a modem 16 processor—can avoid requiring a non-volatile memory for each processor with 17 minimal negative performance impact.

18

### U.S. Patent No. 9,535,490

<sup>19</sup> 45. The '490 patent was duly and legally issued on January 3, 2017 and

<sup>20</sup> Qualcomm is the current owner of the '490 patent and has the full and exclusive

<sup>21</sup> right to bring action and recover damages for Apple's infringement of the '490

<sup>22</sup> patent. The '490 patent is valid and enforceable. A copy of the '490 Patent is

<sup>23</sup> attached hereto as Exhibit E.

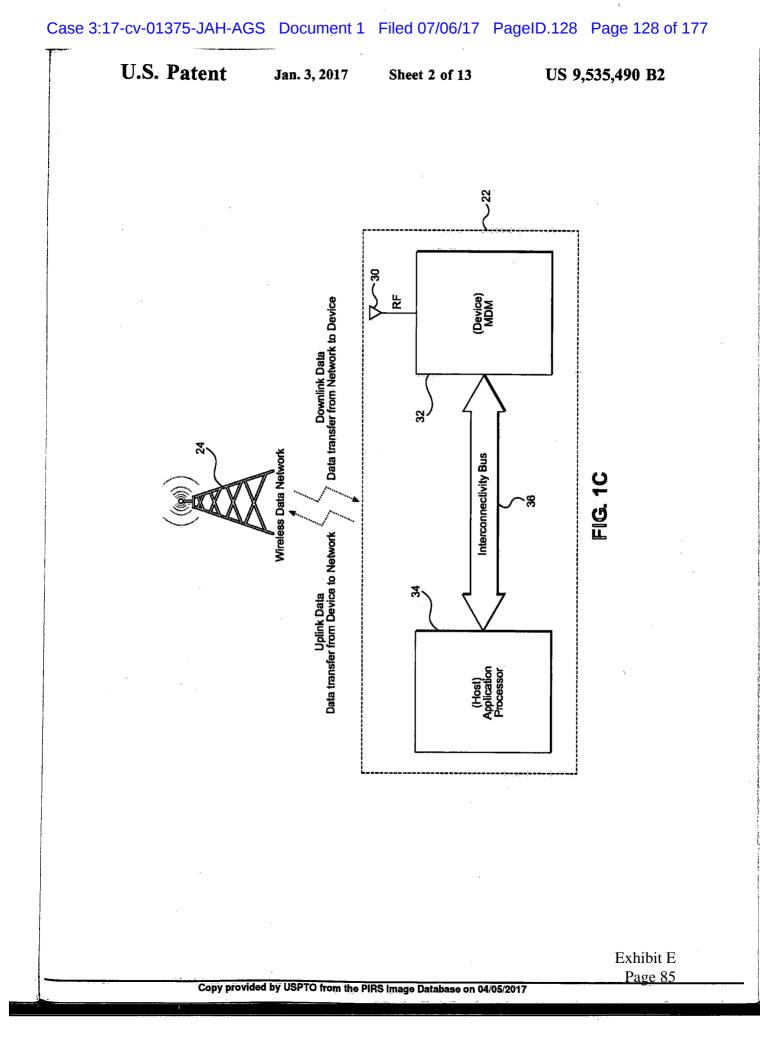

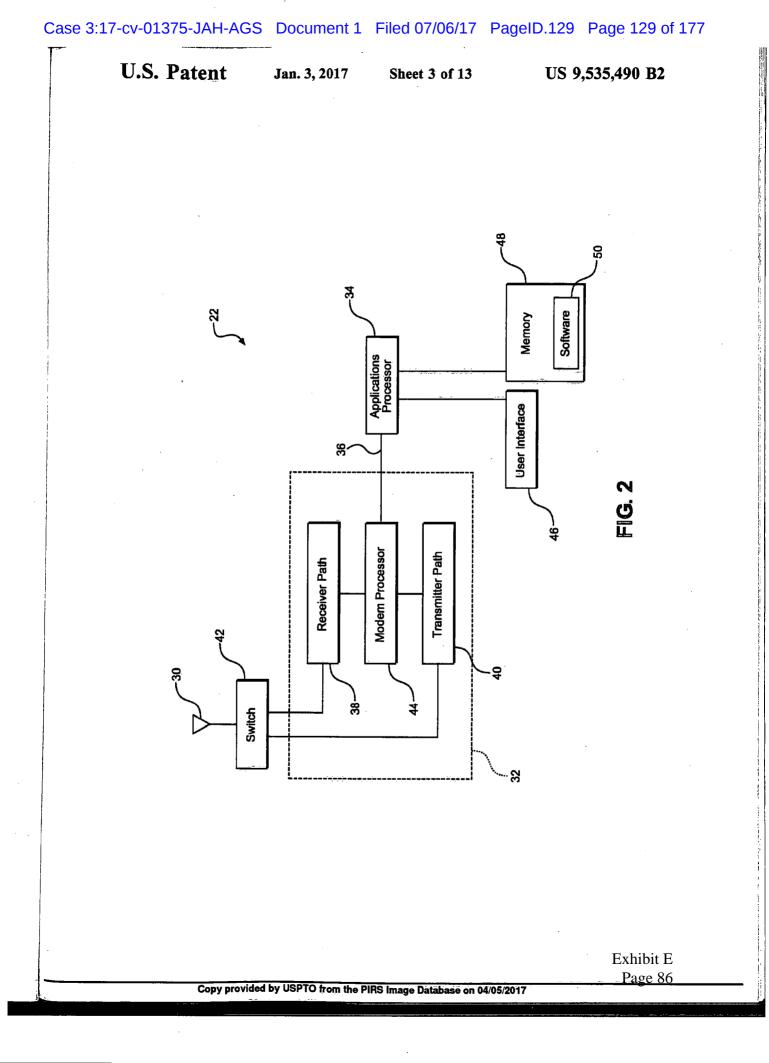

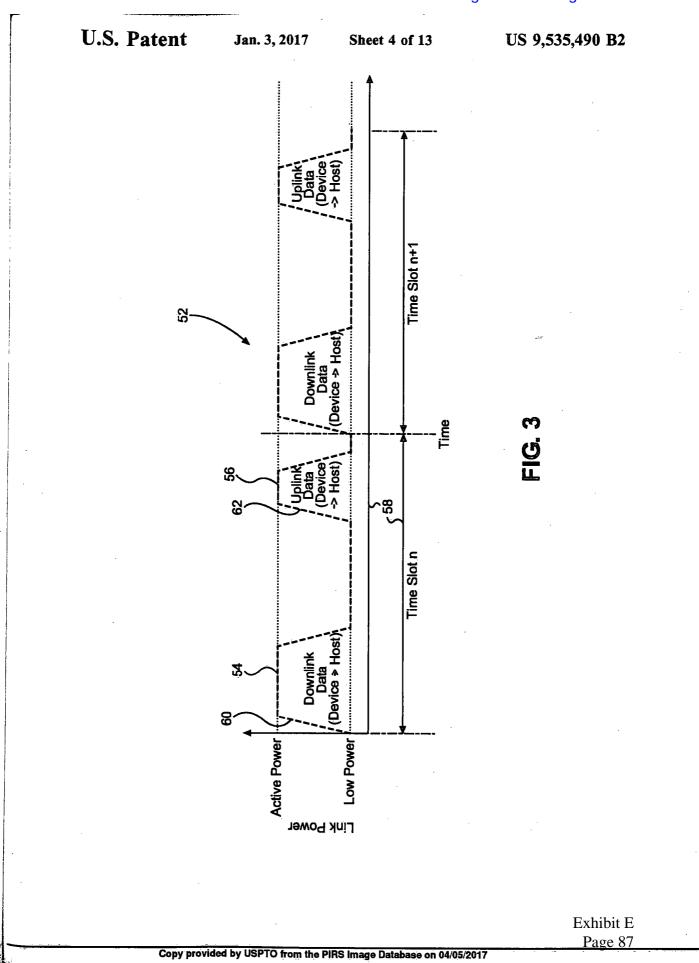

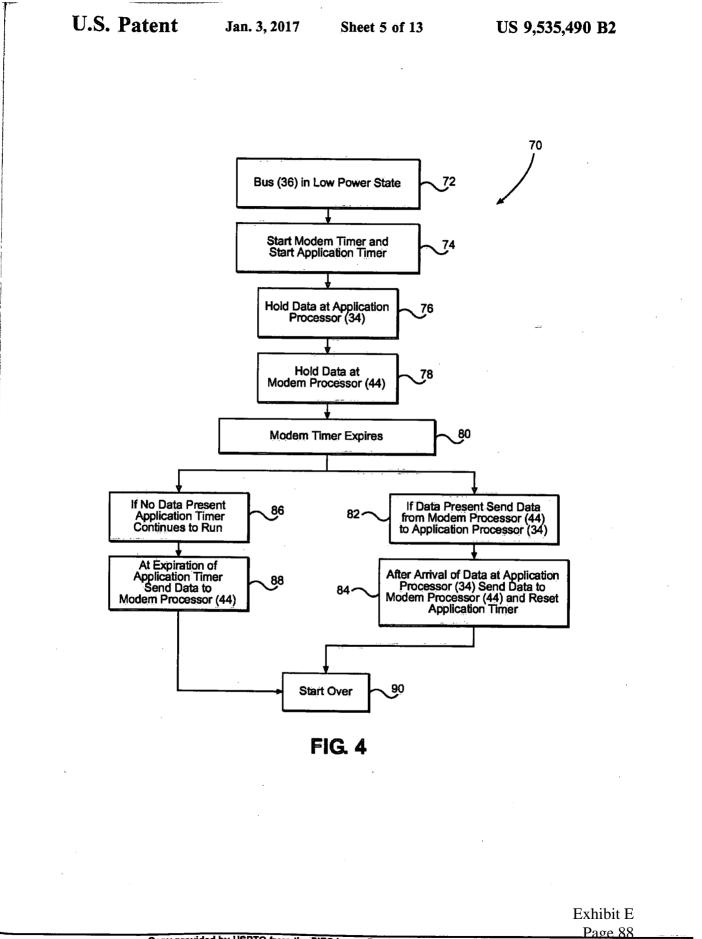

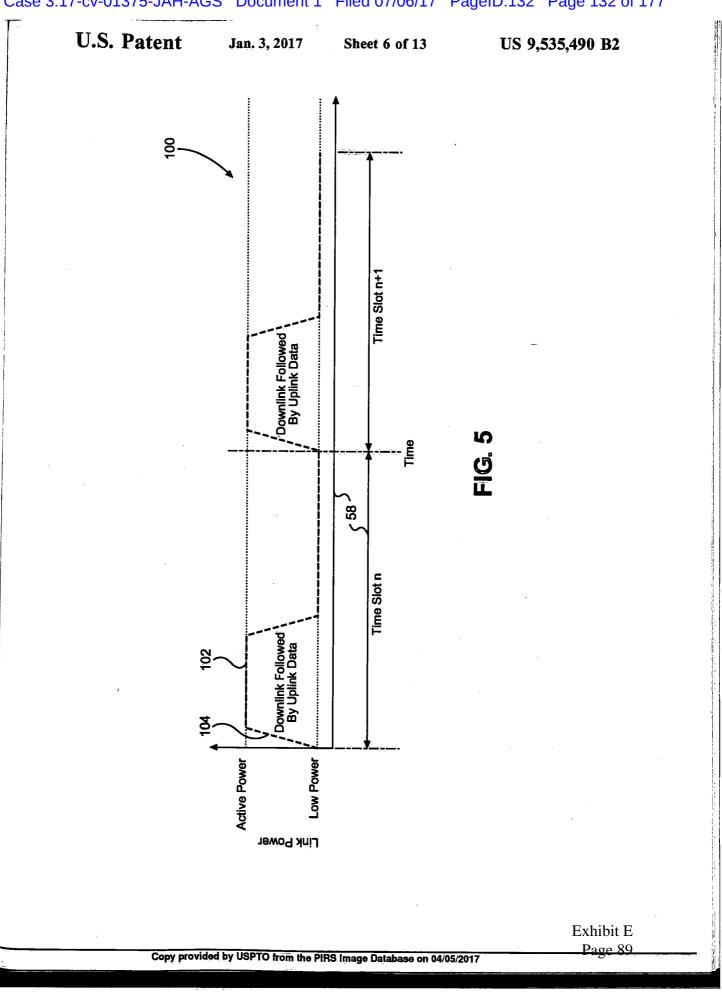

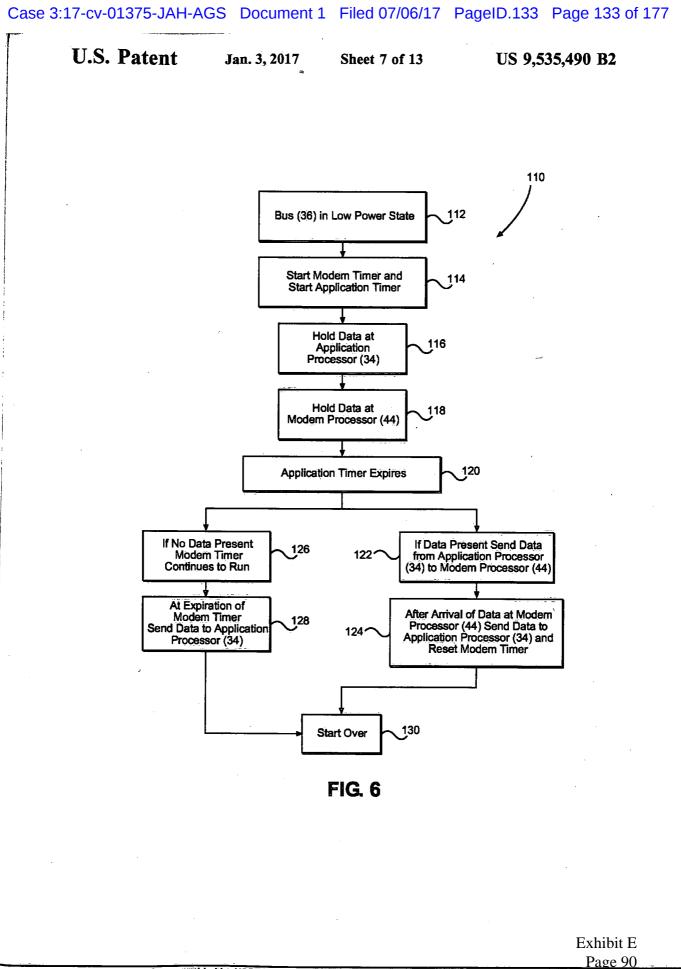

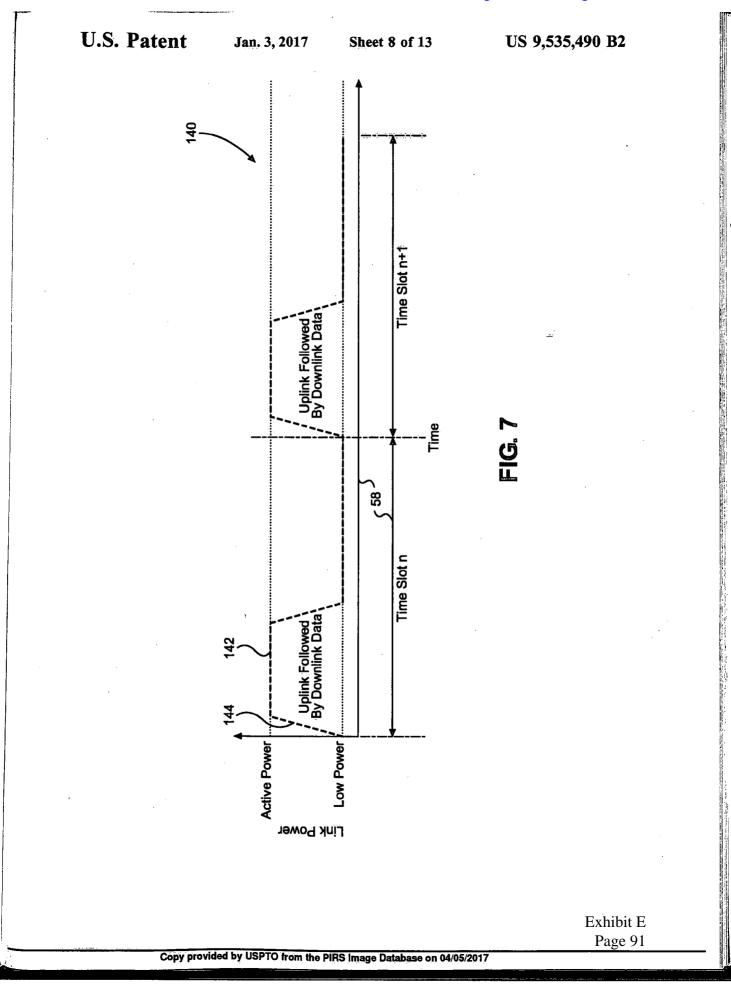

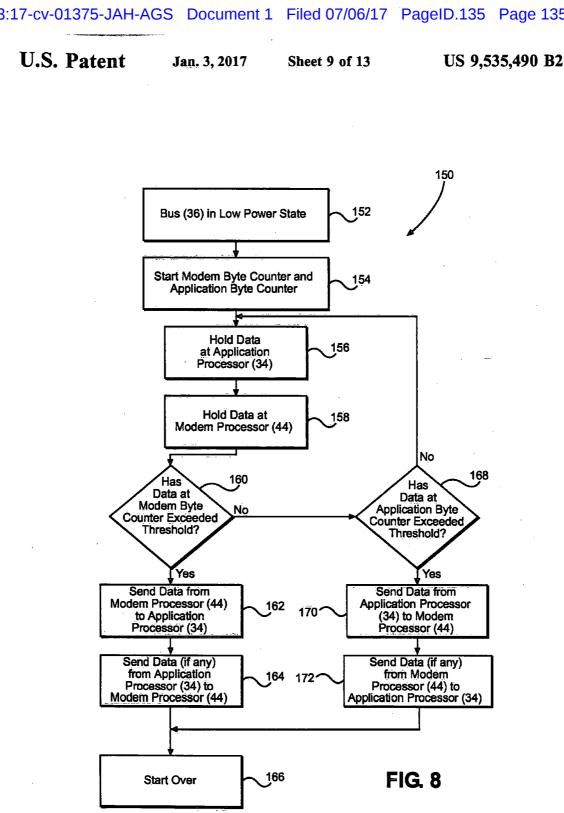

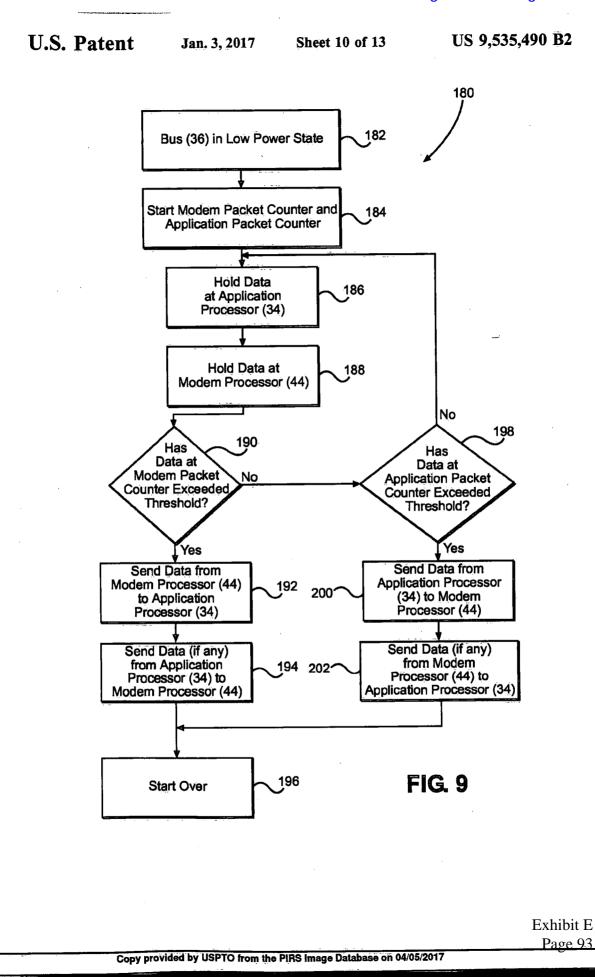

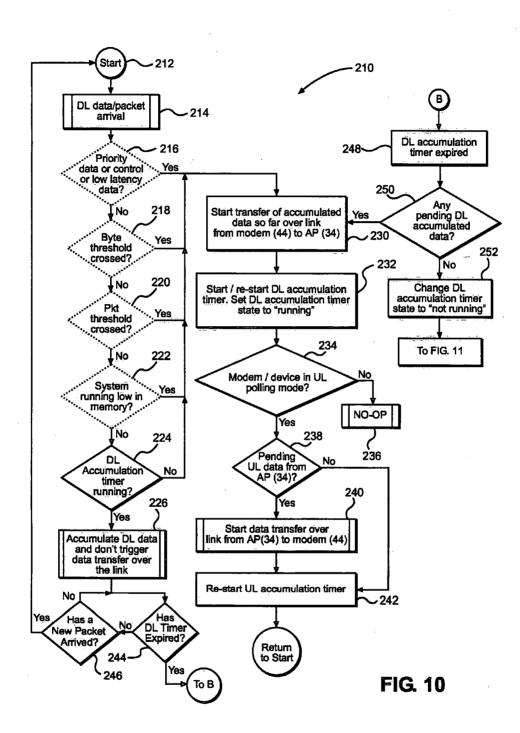

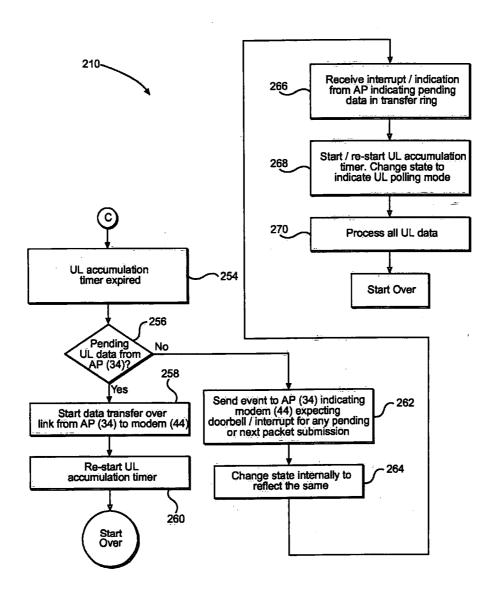

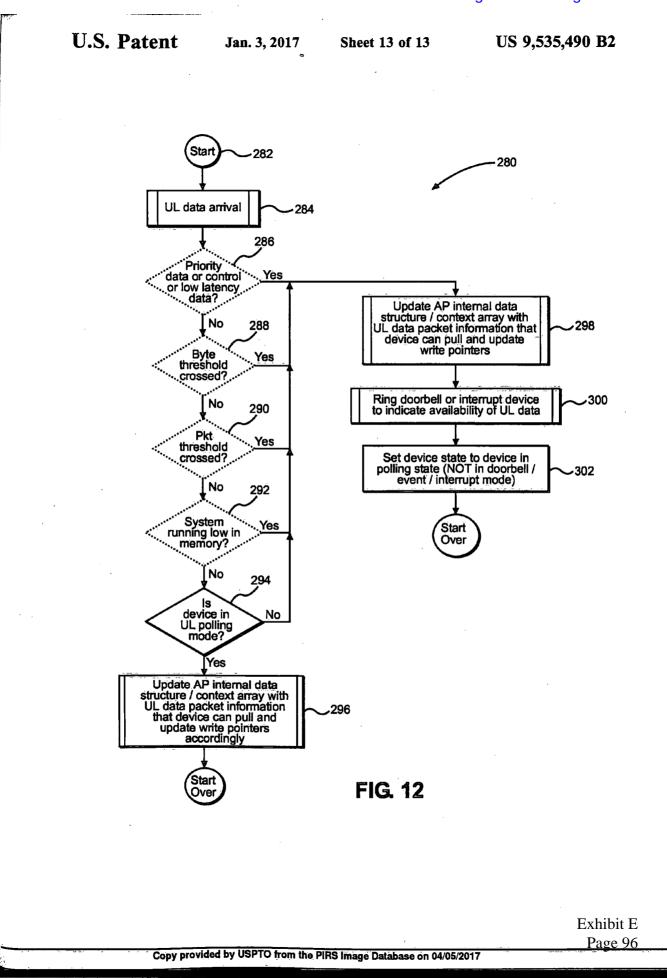

46. The '490 patent relates generally to reducing power consumption in

electronic devices. The '490 patent discloses novel techniques for controlling power

consumption by disclosing methods to minimize the time during which system

buses are in a high-power consumption state. As a result of the invention of the

'490 patent, computing devices can operate just as efficiently with lower power

1 consumption, which in turn prolongs the battery life of those devices.

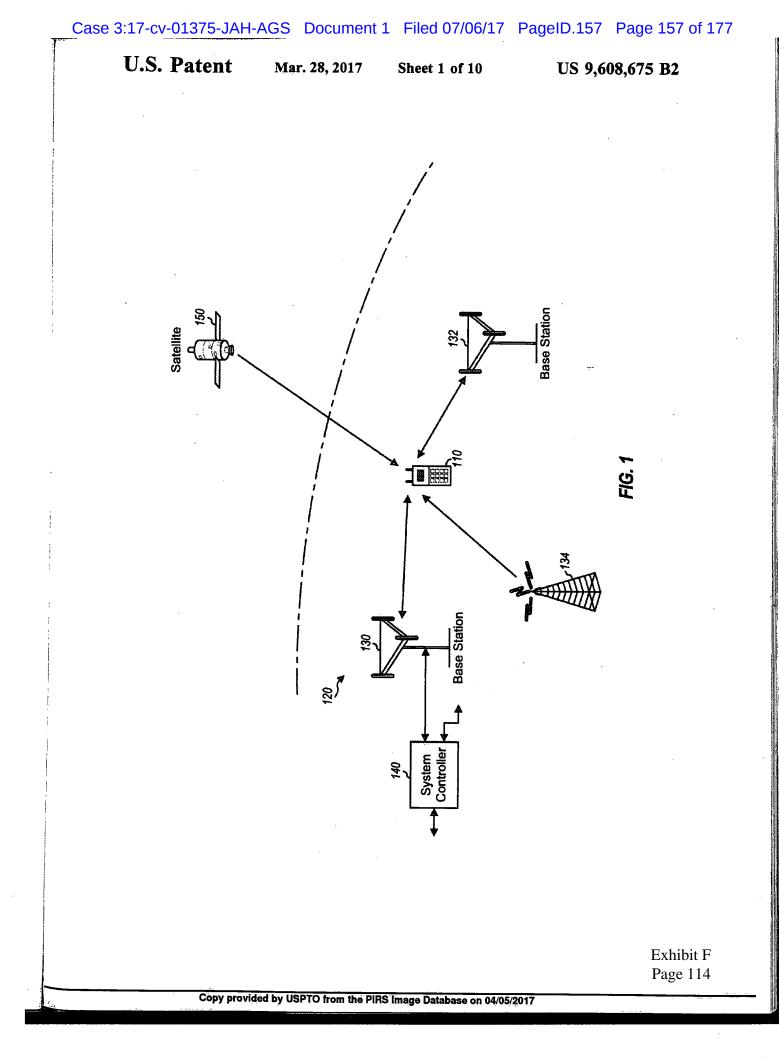

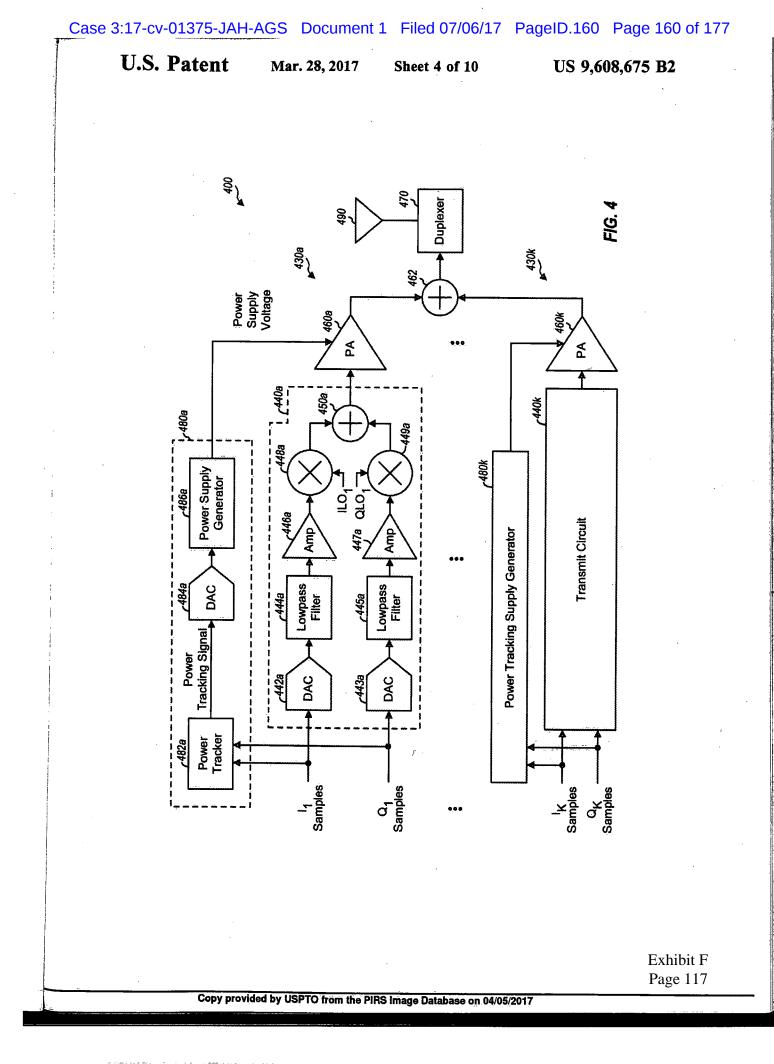

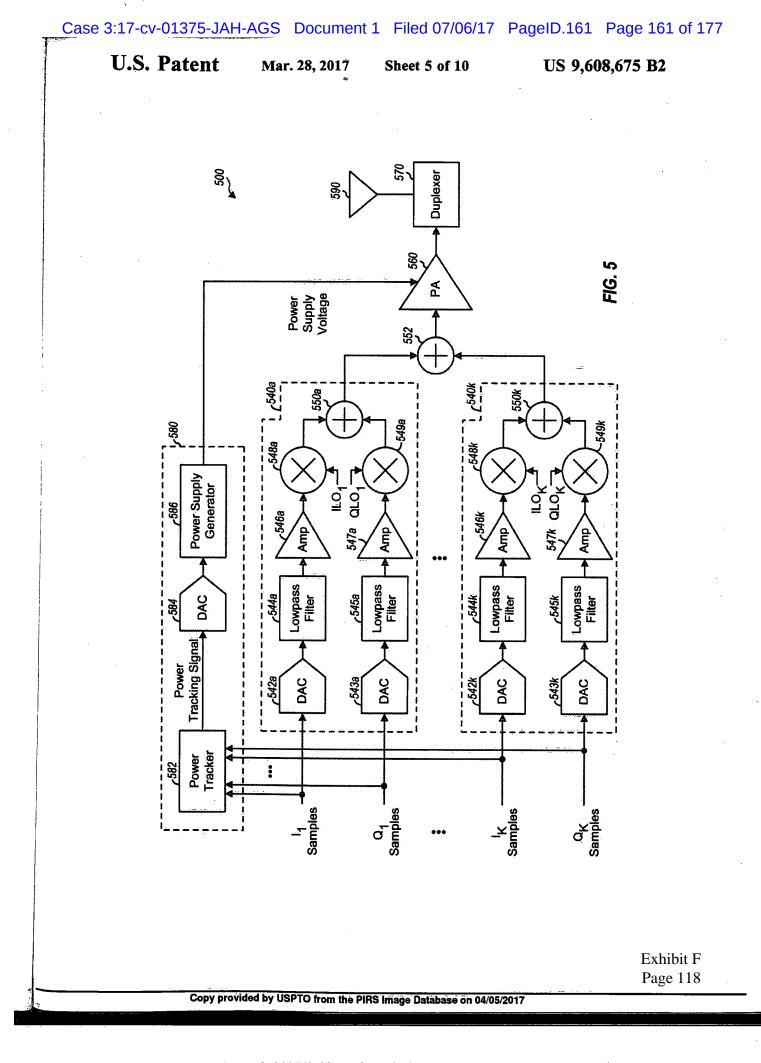

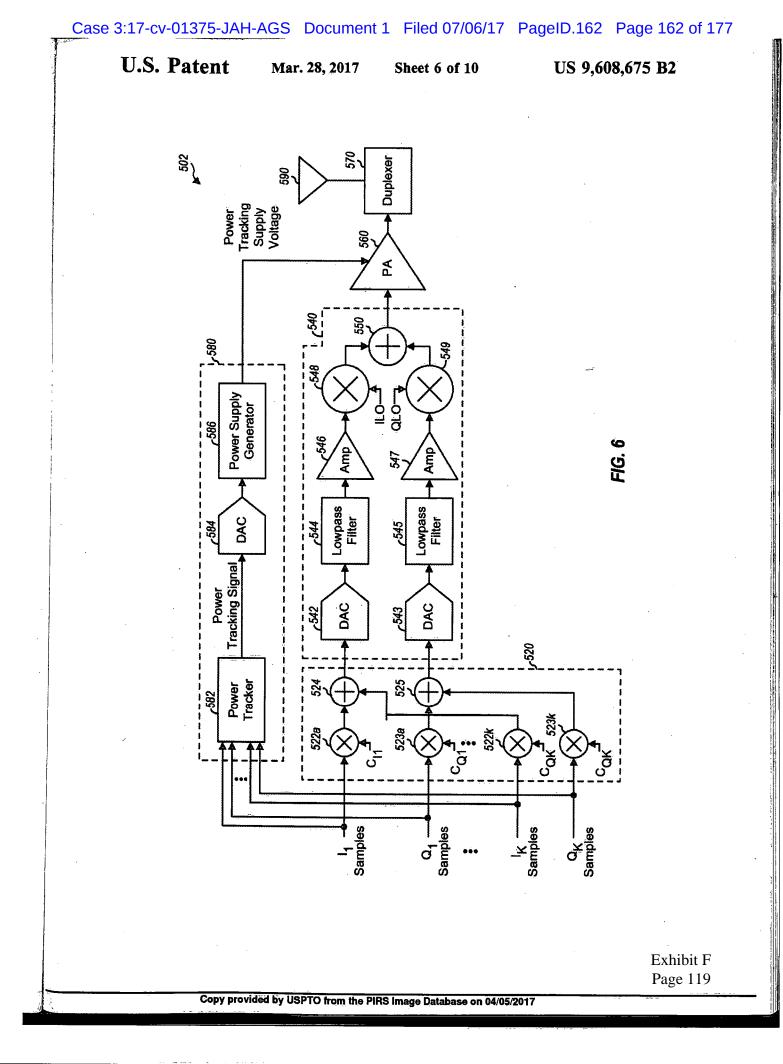

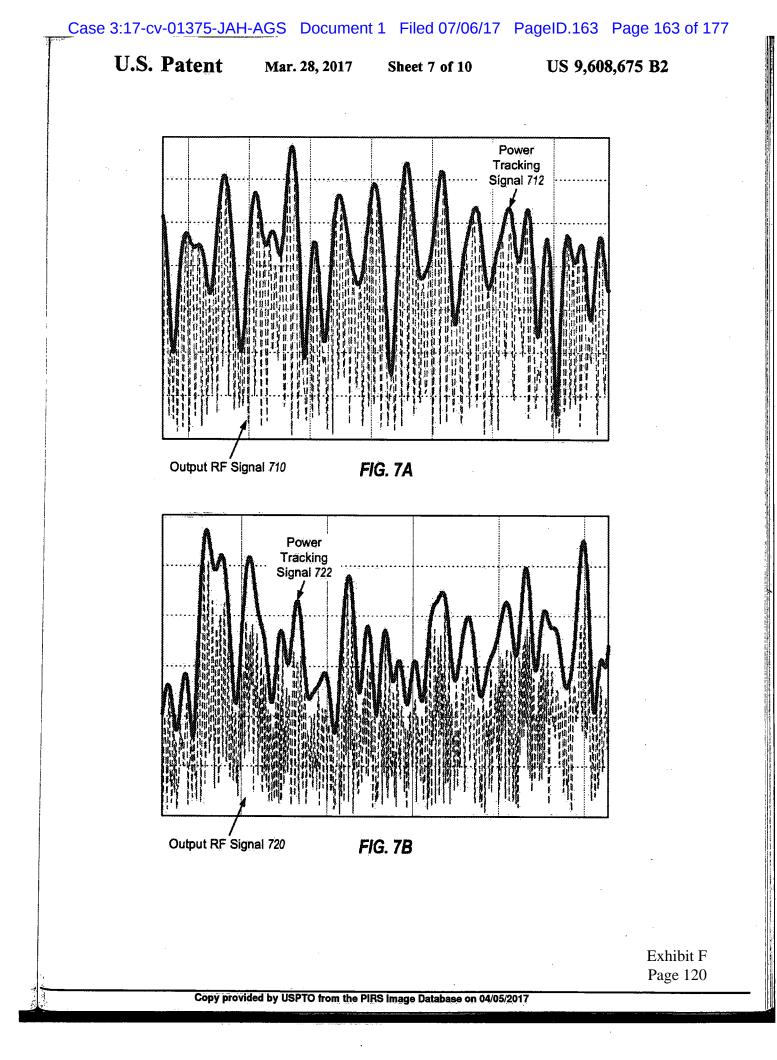

# U.S. Patent No. 9,608,675

47. The '675 patent was duly and legally issued on February 11, 2013 to

Qualcomm, which is the owner of the '675 patent and has the full and exclusive

right to bring action and recover damages for Apple's infringement of the '675

patent. The '675 patent is valid and enforceable. A copy of the '675 Patent is

attached hereto as Exhibit F.

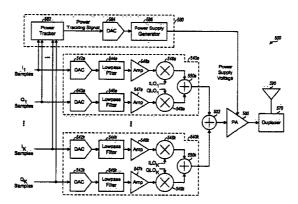

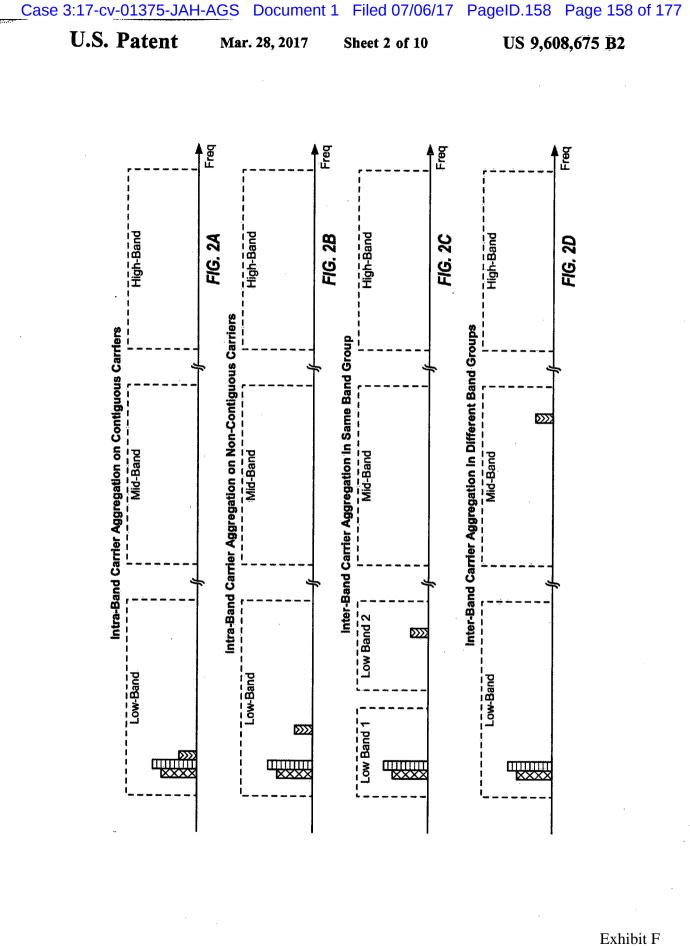

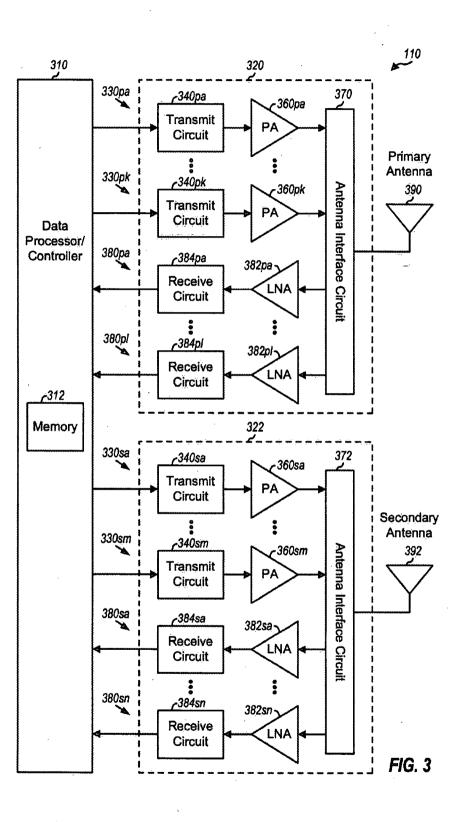

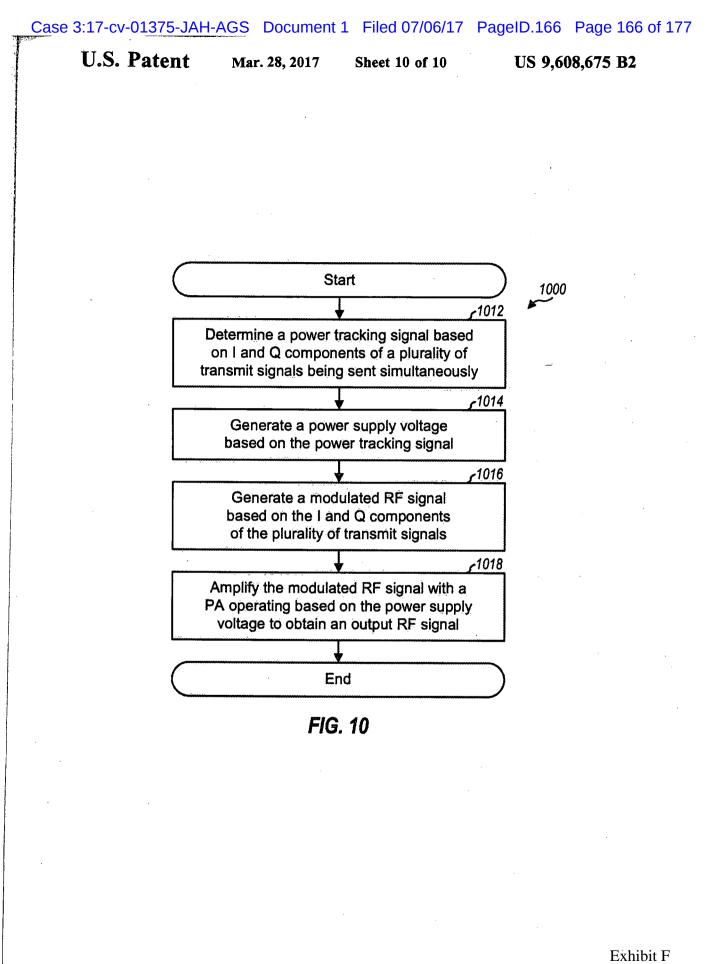

8 48. The '675 patent relates generally to techniques for generating a power 9 supply voltage for a power amplifier that processes multiple transmit signals sent 10 simultaneously, such as multiple transmissions sent simultaneously on multiple 11 carriers at different frequencies. As one example, the '675 patent discloses a power 12 tracker that generates a single power tracking signal based on inputs from a plurality 13 of carrier aggregated transmit signals; a power supply generator for generating a 14 single power supply voltage based on the power tracking signal; and a power 15 amplifier that receives the single power supply voltage and the plurality of carrier 16 aggregated transmit signals to produce a single output RF signal. As one result of 17 the invention of the '675 patent, electronic devices can more efficiently support and 18 perform carrier aggregation.

19

2

# COUNT 1 (PATENT INFRINGEMENT – U.S. PATENT NO. 8,633,936)

20 49. Qualcomm repeats and re-alleges the allegations of paragraphs 1

21 through 48 above as if fully set forth herein.

22 50. Qualcomm is the lawful owner of the '936 patent, and has the full and

23 exclusive right to bring actions and recover damages for Apple's infringement of

24 said patent.

51. In violation of 35 U.S.C. § 271, Apple has been and is still

infringing, contributing to infringement, and/or inducing others to infringe the '936

patent by making, using, offering for sale, selling, or importing iPhone 7 and iPhone

7 Plus devices.

COMPLAINT

-15-

1 52. The accused devices contain a GPU, which is a single-chip, 2 programmable streaming processor. The GPU receives graphic instructions, 3 including an indication of the data precision, and conversion instruction to convert 4 the graphics data to the indicated data precision. Both the graphics and conversion 5 instructions are generated by a compiler. One of many execution units in the GPU is selected due to the indicated data precision and executes the graphic and 6 7 conversion instructions. As a result, the accused devices are able to extend its 8 battery by using lower precision execution units and processing graphics data in a 9 more power efficient manner.

10 53. The accused devices infringe at least claims 1, 10, 11-18, 19, 20-27, 29,

11 38, 49, 55, 56-60, 67, and 68 of the '936 patent.

12 For example, with respect to claims 1, 10, 19, 29, and 38, the accused 54. 13 devices incorporate an Apple A10 GPU, which is a version of the PowerVR 14 GT7600 that is part of the PowerVR Series 7XT GPU line. The Apple A10 GPU 15 receives graphics instructions and executes them within a programmable streaming 16 processor. The indication of the data precision is contained in the graphic instructions, which is generated by the graphics driver's runtime compiler that 17 18 compiles graphics application instructions. On information and belief, Apple 19 designs its own custom shader compiler and driver. The Apple A10 GPU receives 20 conversion instructions, such as "pck" and "unpck" instructions, that are different 21 than the graphics instruction but also generated by the runtime compiler. The 22 conversion instructions are executed by the Apple A10 GPU in order to convert the 23 graphics data associated with the graphics instruction into the indicated data precision. Execution units, such as ALUs, within the processor are selected based 24 25 on the precision required and used to convert the graphics data to the indicated data 26 precision before processing the graphics instruction.

27 55. With respect to claim 11, the accused devices contain further

28 instructions for the Apple A10 GPU to receive the graphics data associated with

graphics instructions, and generate and output a computation result with the

indicated data precision.

56. With respect to claim 12, the accused devices contain further

instructions for selecting an execution unit from a first set of execution units when

the indicated data precision is the first data precision and for selecting an execution

unit fro a second set of execution units when the indicated data precision is the

second data precision, which is different from the first data precision.

8 57. With respect to claim 13, the two data precisions are different such that

9 the first data precision is a full data precision while the second data precision is a

10 half data precision.

58. With respect to claims 14 and 20 the accused devices contain

instructions for different sets of execution units to execute instructions with

corresponding data precision using the graphics data.

14 59. With respect to claim 15, the accused devices contain further

15 instructions to select and use an appropriate execution unit based on the indicated

16 data precision to execute the graphics instructions.

17 60. With respect to claim 16, the accused devices contain further

18 instructions to receive a second, different graphics and conversion instructions to be

19 executed by an execution unit in a second set of execution units with the indicated

20 second data precision.

61. With respect to claim 17, there are instructions programmed to cause

the GPU to decode the graphics instruction in order the determine the indicated data

precision.

24 62. With respect to claim 18, the graphics data associated with the graphics

25 instructions includes at least either vertex graphics data or pixel graphics data.

63. With respect to claim 21, the accused devices contain several execution

units, like ALUs, including at least one full precision execution unit and at least four

half-precision execution units.

COMPLAINT

-17-

64. With respect to claim 22, the controller in the accused devices is

configured to select full-precision execution units when full precision for the

graphics data is required.

4 65. With respect to claim 23, the controller in the accused devices is

5 configured to select half-precision execution units when half precision for the

6 graphics data is required.

66. With respect to claim 24, the accused devices contain at least one fullprecision register bank and four half-precision register banks to store the respective

computation results when the instructions are executed.

67. With respect to claim 25, the accused devices contain at least one fullprecision execution unit and one half-precision execution unit, where, on

information and belief, the full-precision execution unit is shut down when the

indicated data precision is half-precision and the half-precision execution unit will

execute the graphics instruction using the graphics data.

68. With respect to claim 26, the processor in the accused devices contains

a shader processor. On information and belief, Apple designs its own custom shader

compiler and driver.

18 69. With respect to claim 27, the accused devices are wireless

19 communication device handsets.

20 70. With respect to claims 49 and 55, the accused devices will use a 21 compiler executed by a GPU to analyze several application instructions for a 22 graphics application. On information and belief, Apple designs its own custom 23 shader compiler and driver. Each application instruction specifying a first data 24 precision level comprising a full data precision level will cause the compiler to 25 generate corresponding compiled instructions each indicating the full data precision 26 level for execution. Conversion instructions are also generated by the compiler to 27 convert the graphics data from a second, different data precision level to the first 28 data precision level when the compiled instructions are executed.

COMPLAINT

-18-

71. With respect to claim 56, the second data precision level is a half data

2 precision level.

72. With respect to claim 57, the accused devices contain instructions

where compiled instructions indicating a full data precision level is generated when

a corresponding application instruction specifies the full data precision level for its

execution.

7 73. With respect to claim 58, the accused devices contain instructions

8 where compiled instructions indicating a half data precision level is generated when

9 a corresponding application instruction specifies the half data precision level for its

10 execution.

11 74. With respect to claim 59, the accused devices contain instructions

12 where the compiler will generate compiled instructions with predefined field to

13 include information regarding the first data precision level when the corresponding

14 application instruction specifies the first data precision level for its execution.

75. With respect to claim 60, the accused devices contain instructions to

cause the GPU to store the generated compiled instructions in memory for

subsequent execution.

18 76. With respect to claim 67, the accused devices contain executable 19 instructions that are generated by a compiler and can support at least one function of 20 a graphics application. Each executable instruction indicates the first data precision 21 level for its execution. The second data precision level is included in each second 22 executable instruction and is different from the first prevision level, which 23 comprises a full data precision level. Each third executable instructions support at 24 least a function of the graphics application and converts the graphics data from the 25 second data precision level to the first data precision level when the first executable 26 instructions are executed.

27

27

77. With respect to claim 68, the second data precision level is claim 67 is

28

28

28

28

28

28

28

28

28

28

28

29

20

20

21

22

23

24

25

26

27

27

28

28

28

28

29

29

20

20

21

22

23

24

25

26

27

27

28

28

28

28

28

29

20

20

21

21

22

23

24

24

25

26

27

27

27

27

27

28

28

28

29

20

20

21

21

22

23

24

24

25

26

27

27

27

28

28

28

29

20

21

21

21

22

23

24

24

25

26

27

27

27

28

28

28

29

29

20

20

20

21

21

22

23

24

24

25

26

27

27

27

28

28

28

29

20

20

21

21

21

22

23

24

24

25

26

27

27

28

28

28

29

29

20

20

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

COMPLAINT

-19-

1 78. On information and belief, Apple also knowingly induces and/or 2 contributes to the infringement of at least claims 1 and 49 of the '936 patent by 3 others. On information and belief, Apple has had knowledge of the '936 patent, and 4 its infringement of the '936 patent, at least since the time this lawsuit was filed. On 5 information and belief, Apple tests, demonstrates, or otherwise operates the accused devices in the United States, thereby performing the claimed methods and directly 6 7 infringing any asserted claims of the '936 patent requiring such operation. 8 Similarly, Apple's customers and the end users of the accused devices test and/or 9 operate the accused devices in the United States in accordance with Apple's 10 instructions contained in, for example, its user manuals, thereby also performing the 11 claimed methods and directly infringing the asserted claims of the Asserted Patents 12 requiring such operation.

13 79. Apple also contributes to infringement of the '936 patent by selling for importation into the United States, importing into the United States, and/or selling 14 15 within the United States after importation the accused devices and the non-staple 16 constituent parts of those devices, which are not suitable for substantial non-17 infringing use and which embody a material part of the invention described in the 18 '936 patent. These mobile electronic devices are known by Apple to be especially 19 made or especially adapted for use in the infringement of the '936 patent. Apple 20 also contributes to the infringement of the '936 patent by selling for importation into 21 the United States, importing into the United States, and/or selling within the United 22 States after importation components, such as the chipsets or software containing the 23 infringing functionality, of the accused devices, which are not suitable for 24 substantial non-infringing use and which embody a material part of the invention 25 described in the '936 patent. These mobile devices are known by Apple to be 26 especially made or especially adapted for use in the infringement of the '936 patent. 27 Specifically, on information and belief, Apple sells the accused devices to resellers, retailers, and end users with knowledge that the devices are used for infringement. 28

COMPLAINT

-20-

1 End users of those mobile electronic devices directly infringe the '936 patent.

2 80. Apple's acts of infringement have occurred within this district and

3 elsewhere throughout the United States.

- 4 81. Qualcomm has been damaged and will suffer additional damages and

5 irreparable harm unless Apple is enjoined from further infringement. Qualcomm

6 will prove its irreparable harm and damages at trial.

- 7

# COUNT 2 (PATENT INFRINGEMENT – U.S. PATENT NO. 8,698,558)

8 82. Qualcomm repeats and re-alleges the allegations of paragraphs 1

9 through 81 above as if fully set forth herein.

10 83. Qualcomm is the lawful owner of the '558 patent and has the full and

11 exclusive right to bring actions and recover damages for Apple's infringement of

12 said patent.

13 84. In violation of 35 U.S.C. § 271, Apple has been and is still infringing,

14 contributing to infringement, and/or inducing others to infringe the '558 patent by

15 making, using, offering for sale, selling, or importing devices that practice the

16 patent, such as mobile devices including but not limited to iPhone 7 and iPhone 7

17 Plus devices.

18 85. The accused devices infringe at least claims 1 and 6-20 of the '558 19 patent. For example, with respect to claim 1, the accused devices incorporate a 20 Qorvo 81003M Envelope Tracker Modulator, which includes a boost converter. 21 The boost converter receives a supply voltage and generates a signal with an 22 increased voltage. The devices further include an envelope amplifier that receives 23 an envelope signal and a boosted supply voltage. The envelope amplifier generates a second supply voltage based on the envelope signal and the boosted supply 24 25 voltage. The envelope amplifier receives a supply voltage and generates a second 26 supply voltage based on the first supply voltage or the boosted supply voltage. The 27 envelope amplifier includes an operational amplifier that receives an envelope signal 28 and amplifies a signal, a driver that receives an amplified signal and provides

multiple control signals, a PMOS transistor with a gate receiving a control signal, a

source receiving a boosted supply voltage or a supply voltage and a drain providing

a supply voltage, and a NMOS transistor having a gate receiving a control signal, a

drain providing a supply voltage, and a source coupled to a ground.

5 With respect to claim 6, a power amplifier receives and amplifies an 86. 6 input radio frequency signal to provide an amplified output signal. The device also 7 includes a supply generator for receiving an envelope signal and supply voltage and 8 generating a boosted supply voltage. The supply generator incorporates an 9 operational amplifier to receive the envelope signal and provide an amplified signal, 10 a driver that receives the amplified signal and provides a first control signal and a 11 second control signal, a P-channel metal oxide semiconductor (PMOS) transistor, 12 which has a gate receiving a first control signal, a source receiving the boosted 13 supply voltage or the first supply voltage and a drain providing the second supply 14 voltage, and an N-channel metal oxide semiconductor (NMOS) transistor having a 15 gate receiving the second control signal, a drain providing the second supply 16 voltage, and a source coupled to circuit ground.

17 87. With respect to claim 7, the accused devices include a supply generator

18 that generates the second supply voltage based on the envelope signal and either the

19 boosted supply voltage or the first supply voltage.

20 88. With respect to claim 8, the accused devices generate a boosted supply 21 voltage based on a first supply voltage, where the boosted supply voltage has a 22 higher voltage than the first supply voltage. Further, the devices generate a second 23 supply voltage based on an envelope signal and the boosted supply voltage. The 24 devices have a second supply voltage that is generated by an envelope amplifier that 25 produces the second supply voltage using an operational amplifier (op-amp) that 26 receives the envelope signal and provides an amplified signal, a driver that receives 27 the amplified signal and provides a first control signal and a second control signal, a 28 P-channel metal oxide semiconductor (PMOS) transistor that receives the first

COMPLAINT

-22-

1 control signal, a source that receives the boosted supply voltage or the first supply 2 voltage, and a drain providing the second supply voltage and an N-channel metal 3 oxide semiconductor (NMOS) transistor that receives the second control signal at a gate and provides a second supply voltage through a drain, and a source for circuit 4 5 grounding.

89. 6 With respect to claim 9, the accused devices generate the second supply 7 voltage based on the envelope signal and either the boosted supply voltage or the 8 first supply voltage.

9 90. With respect to claim 10, the accused devices are used for generating a 10 boosted supply voltage based on a first supply voltage, the boosted supply voltage 11 having a higher voltage than the first supply voltage. The accused devices are also 12 used for generating a second supply voltage based on the envelope signal and the 13 boosted supply voltage. The accused devices are also used for generating the 14 second supply voltage incorporating an envelope amplifier that produces the second 15 supply voltage using an operational amplifier that receives the envelope signal and 16 provides an amplified signal, a driver that receives the amplified signal and provides 17 a first control signal and a second control signal, a P-channel metal oxide 18 semiconductor (PMOS) transistor that receives the first control signal, a source that 19 receives the boosted supply voltage or the first supply voltage, and a drain providing 20 the second supply voltage and an N-channel metal oxide semiconductor (NMOS) 21 transistor that receives the second control signal at a gate and provides a second 22 supply voltage through a drain, and a source for circuit grounding.

23

91. With respect to claim 11, the accused devices are used for generating 24 the second supply voltage based on an envelope signal and either the boosted supply 25 voltage or the first supply voltage.

26 92. With respect to claim 12, the accused devices include a switcher 27 operative to receive a first supply voltage and provide a first supply current and an 28 envelope amplifier operative to receive an envelope signal and provide a second

### COMPLAINT

-23-

1 supply current based on the envelope signal. The power amplifier is operative to 2 receive a total supply current comprising the first supply current and the second supply current, wherein the switcher comprises a current sense amplifier operative 3 4 to sense the first supply current, or the second supply current, or the total supply 5 current and provide a sensed signal. The accused devices also include a driver 6 operative to receive the sensed signal and provide a first control signal and a second 7 control signal; a P-channel metal oxide semiconductor (PMOS) transistor having a 8 gate receiving the first control signal, a source receiving the first supply voltage, and 9 a drain providing a switching signal for an inductor providing the first supply 10 current; and an N-channel metal oxide semiconductor (NMOS) transistor having a 11 gate receiving the second control signal, a drain providing the switching signal, and 12 a source coupled to circuit ground.

13 93. With respect to claim 13, the accused devices include a boost converter

14 operative to receive the first supply voltage and provide a boosted supply voltage

15 having a higher voltage than the first supply voltage, wherein the envelope amplifier

16 operates based on the first supply voltage or the boosted supply voltage.

With respect to claim 14, the accused devices include a first supply

current that comprises direct current (DC) and low frequency components, and the

second supply current comprises higher frequency components.

20With respect to claim 15, the accused devices include an inductor 95. 21 operative to receive a switching signal and provide a supply current. The accused 22 devices also include a switcher operative to sense an input current and generate the 23 switching signal to charge and discharge the inductor to provide the supply current. The switcher adds an offset to the input current to generate a larger supply current 24 25 via the inductor than without the offset. The switcher in the accused devices 26 includes a summer that sums the input current and an offset current and provide a 27 summed current. The accused devices include a current sense amplifier operative to 28 receive the summed current and provide a sensed signal. The accused devices also

include a driver operative to receive the sensed signal and provide at least one

control signal used to generate the switching signal for the inductor.

3 96. With respect to claim 16, in the accused devices the switcher operates

4 based on a first supply voltage, where an offset is determined based on the first

5 supply voltage.

97. With respect to claim 17, the accuse devices contain a first control

signal and a second control signal, where the switcher includes a P-channel metal

oxide semiconductor (PMOS) transistor having a gate receiving the first control

signal, a source receiving a first supply voltage, and a drain providing the switching

signal, and an N-channel metal oxide semiconductor (NMOS) transistor having a

gate receiving the second control signal, a drain providing the switching signal, and

a source coupled to circuit ground.

13 98. With respect to claim 18, the accused devices include an envelope

14 amplifier that receives an envelope signal and provides a second supply current

15 based on the envelope signal, where a total supply current comprises the supply

16 current from the switcher and the second supply current from the envelope

17 amplifier.

18 99. With respect to claim 19, the accused devices include a boost converter

19 operative to receive the first supply voltage and provide a boosted supply voltage

20 having a higher voltage than the first supply voltage, where the envelope amplifier

21 operates based on the first supply voltage or the boosted supply voltage.

100. With respect to claim 20, the accused devices include a power amplifier

so that the accused devices can receive the supply current from the inductor and

receive and amplify an input radio frequency (RF) signal and provide an output RF

signal.

26 101. On information and belief, Apple also knowingly induces and/or

27 contributes to the infringement of at least claims 8-9 of the '558 patent by others.

28 On information and belief, Apple has had knowledge of the '558 patent, and its

infringement of the '558 patent, at least since the time this lawsuit was filed.

2 Additionally, Qualcomm has provided technical assistance and solutions to Apple, 3 including envelope tracking technology, under non-disclosure agreements. Apple 4 was aware of, and implemented, Qualcomm's technology in certain of its devices 5 without authorization. On information and belief, Apple tests, demonstrates, or 6 otherwise operates the accused devices in the United States, thereby performing the 7 claimed methods and directly infringing any asserted claims of the '558 patent 8 requiring such operation. Similarly, Apple's customers and the end users of the 9 accused devices test and/or operate the accused devices in the United States in 10 accordance with Apple's instructions contained in, for example, its user manuals, 11 thereby also performing the claimed methods and directly infringing the asserted 12 claims of the Asserted Patents requiring such operation.

13 102. Apple also contributes to infringement of the '558 patent by selling for importation into the United States, importing into the United States, and/or selling 14 15 within the United States after importation the accused devices and the non-staple 16 constituent parts of those devices, which are not suitable for substantial non-17 infringing use and which embody a material part of the invention described in the 18 '558 patent. These mobile electronic devices are known by Apple to be especially 19 made or especially adapted for use in the infringement of the '558 patent. Apple 20 also contributes to the infringement of the '558 patent by selling for importation into 21 the United States, importing into the United States, and/or selling within the United 22 States after importation components, such as the chipsets or software containing the 23 infringing functionality, of the accused devices, which are not suitable for 24 substantial non-infringing use and which embody a material part of the invention 25 described in the '558 patent. These mobile devices are known by Apple to be 26 especially made or especially adapted for use in the infringement of the '558 patent. 27 Specifically, on information and belief, Apple sells the accused devices to resellers, retailers, and end users with knowledge that the devices are used for infringement. 28

COMPLAINT

1

-26-

1 End users of those mobile electronic devices directly infringe the '558 patent.

2 103. Apple's acts of infringement have occurred within this district and

3 elsewhere throughout the United States.

4

5

6

104. Qualcomm has been damaged and will suffer additional damages and irreparable harm unless Apple is enjoined from further infringement. Qualcomm will prove its irreparable harm and damages at trial.

7

# COUNT 3 (PATENT INFRINGEMENT – U.S. PATENT NO. 8,487,658)

8 105. Qualcomm repeats and re-alleges the allegations of paragraphs 1

9 through 104 above as if fully set forth herein.

10 106. Qualcomm is the lawful owner of the '658 patent and has the full and

11 exclusive right to bring actions and recover damages for Apple's infringement of

12 said patent.

13 107. In violation of 35 U.S.C. § 271, Apple has been and is still infringing,

14 contributing to infringement, and/or inducing others to infringe the '658 patent by

15 making, using, offering for sale, selling, or importing mobile devices that practice

16 the patent, including but not limited to iPhone 7 and iPhone 7 Plus devices.

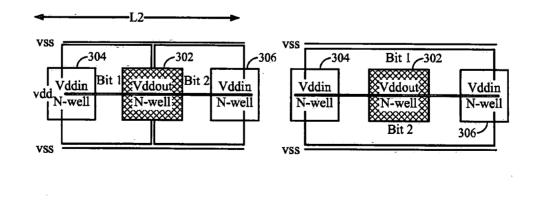

17 108. The accused devices use four-bit voltage level shifters arranged in a

18 certain layout to reduce the area of the four-bit voltage level shifters. Each bit is

19 shifted from a first voltage level logic to a second voltage level logic by forming

20 four one-bit voltage level shifter circuit, where each one-bit voltage level shifter

21 circuit is formed over two N-wells.

109. The accused devices infringe at least claims 9, 12, 14, 20, 21 and 22 of

the '658 patent.

110. For example, with respect to claim 9, the accused devices each include

a Qorvo ET modulator, which includes four voltage level shift (VLS) circuits. Each

VLS circuit shifts a bit from a first voltage level logic to a second voltage level

logic. The Qorvo ET modulator includes 3 N-wells formed in the substrate, with the

second and third N-well adjacent to the first N-well but also opposite from each

other. The four-bit multi-voltage circuit of the Qorvo ET modulator includes four

one-bit VLS circuit, each of which is formed on two N-wells.

3 111. With respect to claim 12, the accused devices have the first, second and

4 third N-wells arranged in a row with the first N-well at a center position.

5 112. With respect to claim 14, the accused devices have the first N-well

6 biased at the first voltage level, and the second and third N-wells biased at the

7 second voltage level.

8 113. With respect to claim 20 of the '658 patent, the accused devices

9 perform the method of reducing die area and switching power in the four-bit multi10 voltage circuit in the Qorvo ET modulator by shifting each of the four bits from a

11 first voltage level logic to a second voltage level logic. To achieve this, three N12 wells are formed where the second and third N-well are each adjacent to the first N13 well and opposite from each other. Then, four one-bit VLS circuits are formed,

14 each covering a portion of two N-wells.

15 114. With respect to claim 21 of the '658 patent, the accused devices contain

a Qorvo ET modulator, which reduces the die area and switching power in the fourbit multi-voltage circuit to shift each of the four bits from the first voltage level

logic to the second voltage level logic by forming three N-wells in the substrate,

where the second and third N-wells are each adjacent to the first N-well and

opposite of each other. Logic is configured to form four one-bit VLS circuit, each

of which covers a portion of two N-wells.

115. With respect to claim 22 of the '658 patent, the accused devices contain

a Qorvo ET modulator, which reduces the die area and switching power in the fourbit multi-voltage circuit to shift each of the four bits from the first voltage level

logic to the second voltage level logic by forming three N-wells in the substrate,

where the second and third N-wells are each adjacent to the first N-well and

opposite of each other. The Qorvo ET modulator also has means for forming four

one-bit VLS circuit, each of which covers a portion of two N-wells.

COMPLAINT

-28-

1 116. Apple's acts of infringement have occurred within this district and

2 elsewhere throughout the United States.

3 117. Qualcomm has been damaged and will suffer additional damages and

4 irreparable harm unless Apple is enjoined from further infringement. Qualcomm

5 will prove its irreparable harm and damages at trial.

6

# COUNT 4 (PATENT INFRINGEMENT – U.S. PATENT NO. 8,838,949)

7 118. Qualcomm repeats and re-alleges the allegations of paragraphs 1

8 through 117 above as if fully set forth herein.

9 119. Qualcomm is the lawful owner of the '949 patent, and has the full and

10 exclusive right to bring actions and recover damages for Apple's infringement of

11 said patent.

12 120. In violation of 35 U.S.C. § 271, Apple has been and is still infringing,

13 contributing to infringement, and/or inducing others to infringe the '949 patent by

14 making, using, offering for sale, selling, or importing mobile devices that practice

15 the patent, including but not limited to iPhone 7 and iPhone 7 Plus devices.

16 121. The accused devices allow a secondary processor that does not have its

17 own flash memory to boot up. For example, an image for the secondary processor is

18 stored in a memory coupled to a primary processor. A scatter loader directly

19 transfers the image from the memory coupled to the primary processor into a

20 memory of the secondary processor, allowing the secondary processor to boot up.

21 122. The accused devices infringe at least claims 1-8, 10-14, 16, 20, and 22

22 of the '949 patent.

123 123. The accused devices infringe claims 1, 10, 16, 20, and 22 of the '949

patent as follows. Each accused device is a multi-processor system. Each accused

device includes a primary processor—an Apple A10 application processor. Each

accused device also includes a secondary processor—a baseband processor. An

interface such as a PCIe interface communicatively couples the primary processor

and the secondary processor. The primary processor is coupled with a memory

COMPLAINT

-29-

1 storing an executable software image for the secondary processor. The secondary 2 processor includes a system memory and a hardware buffer for receiving an image 3 header and at least one data segments of an executable software image. The 4 secondary processor receives the image header and each data segment separately 5 over the interface. The secondary processor includes a scatter loader controller, 6 which is configured to load the image header and scatter load each received data 7 segment based at least in part on the loaded image header directly from the hardware 8 buffer to the system memory of the secondary processor. Thus, the accused devices 9 infringe claims 1, 10, 16, 20, and 22 of the '949 patent.

10 124. With respect to claims 2 and 12 of the '949 patent, the scatter loader controller loads the executable software image directly from the hardware buffer to 11 12 the system memory of the secondary processor without copying data between 13 system memory locations on the secondary processor. Indeed, this is inherent in the 14 scatter loader controller scatter loading each data segment of the executable 15 software image directly on the to the system memory of the secondary processor as 16 recited in claims 1 and 10. Thus, the accused devices infringe claims 2 and 12 of 17 the '949 patent.

18 125. With respect to claim 3 of the '949 patent, the secondary processor

19 receives raw image data of the executable software image via the interface. Thus,

20 the accused devices infringe claim 3 of the '949 patent.

126. With respect to claim 4 of the '949 patent, the secondary processor is

configured to process the image header, which includes destination addresses of

each data segment, to determine at least one location within the system memory of

the secondary processor to store the at least one data segment. Thus, the accused

devices infringe claim 4 of the '949 patent.

26 127. With respect to claim 5 of the '949 patent, the secondary processor is

27 configured to determine the at least one location within the system memory to store

28 that data segment based on the received image header, which includes destination

addresses of each data segment, before receiving that data segment. Thus, the

accused devices infringe claim 5 of the '949 patent.

3 128. With respect to claim 6 of the '949 patent, the secondary processor

4 includes a non-volatile memory such as a boot read only memory (ROM) storing a

5 boot loader that initiates transfer of the executable software images for the

6 secondary processor. Thus, the accused devices infringe claim 6 of the '949 patent.

7 129. With respect to claims 7 and 14 of the '949 patent, the primary

8 processor and the secondary processor are located on different chips. Thus, the

9 accused devices infringe claims 7 and 14 of the '949 patent.

10 130. With respect to claim 8 of the '949 patent, a hardware buffer of a transport mechanism, such as a hardware buffer at endpoint (EP) of a PCIe interface 11 12 that buffers data received from root complex (RC), receives data segments and the 13 scatter loader controller scatter loads the received data segments directly to the 14 system memory of the secondary processor. As the hardware buffer at the EP of a 15 PCIe interface does not have the capacity to store an entire executable software image, the secondary processor loads a portion of the executable software image 16 17 into its system memory without an entire executable software image being stored in 18 the hardware buffer. Thus, the accused devices infringe claim 8 of the '949 patent.

19 131. With respect to claim 11 of the '949 patent, the accused devices each

20 boot the secondary processor using the executable software image. Thus, the

21 accused devices infringe claim 11 of the '949 patent.

132. With respect to claim 13 of the '949 patent, the accused devices each

processes the image header prior to the loading of each data segment. Thus, the

accused devices infringe claim 13 of the '949 patent.

133. On information and belief, Apple also knowingly induces and/or

contributes to the infringement of at least claims 10-14 and 22 of the '949 patent by

others. On information and belief, Apple has had knowledge of the '949 patent, and

its infringement of the '949 patent, at least since the time this lawsuit was filed.

1 Additionally, Qualcomm has provided technical assistance and solutions to Apple 2 under non-disclosure agreements. Apple was aware of, and implemented, 3 Qualcomm's technology in certain of its devices without authorization. On 4 information and belief, Apple tests, demonstrates, or otherwise operates the accused 5 devices in the United States, thereby performing the claimed methods and directly infringing any asserted claims of the '949 patent requiring such operation. 6 7 Similarly, Apple's customers and the end users of the accused devices test and/or 8 operate the accused devices in the United States in accordance with Apple's 9 instructions contained in, for example, its user manuals, thereby also performing the 10 claimed methods and directly infringing the asserted claims of the Asserted Patents 11 requiring such operation.

134. Apple also contributes to infringement of the '949 patent by selling for 12 13 importation into the United States, importing into the United States, and/or selling 14 within the United States after importation the accused devices and the non-staple constituent parts of those devices, which are not suitable for substantial non-15 16 infringing use and which embody a material part of the invention described in the 17 '949 patent. These mobile electronic devices are known by Apple to be especially 18 made or especially adapted for use in the infringement of the '949 patent. Apple 19 also contributes to the infringement of the '949 patent by selling for importation into 20 the United States, importing into the United States, and/or selling within the United 21 States after importation components, such as the chipsets or software containing the 22 infringing functionality, of the accused devices, which are not suitable for 23 substantial non-infringing use and which embody a material part of the invention 24 described in the '949 patent. These mobile devices are known by Apple to be 25 especially made or especially adapted for use in the infringement of the '949 patent. Specifically, on information and belief, Apple sells the accused devices to resellers, 26 27 retailers, and end users with knowledge that the devices are used for infringement. 28 End users of those mobile electronic devices directly infringe the '949 patent.

COMPLAINT

-32-

1 135. Apple's acts of infringement have occurred within this district and

2 elsewhere throughout the United States.

3 136. Qualcomm has been damaged and will suffer additional damages and

4 irreparable harm unless Apple is enjoined from further infringement. Qualcomm

5 will prove its irreparable harm and damages at trial.

6

# COUNT 5 (PATENT INFRINGEMENT – U.S. PATENT NO. 9,535,490)

7 137. Qualcomm repeats and re-alleges the allegations of paragraphs 1

8 through 136 above as if fully set forth herein.

- 9 138. Qualcomm is the lawful owner of the '490 patent, and has the full and

10 exclusive right to bring actions and recover damages for Apple's infringement of

11 said patent.

- 12 139. In violation of 35 U.S.C. § 271, Apple has been and is still infringing,

13 contributing to infringement, and/or inducing others to infringe the '490 patent by

14 making, using, offering for sale, selling, or importing devices that practice the

15 patent, including but not limited to iPhone 7 and iPhone 7 Plus devices.