# **Prospect for New Memory Technology**

Sung Wook Park SK hynix Aug, 2012

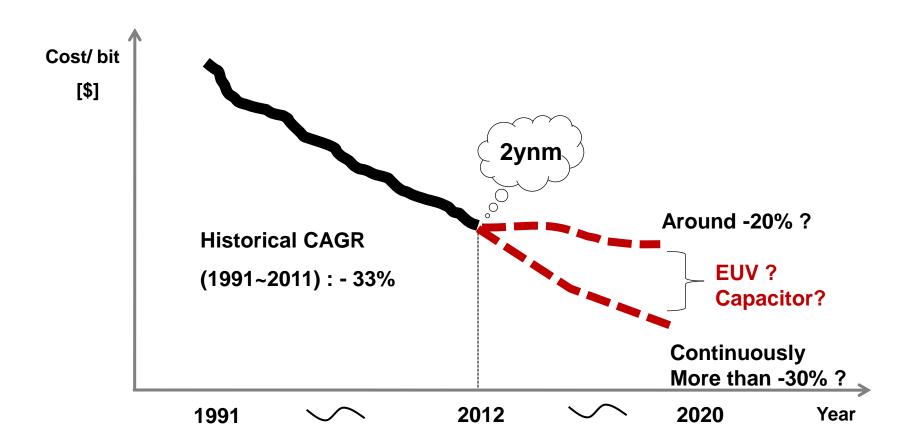

### **DRAM Cost Trend**

### **Cost per Giga Bit - Past and Future**

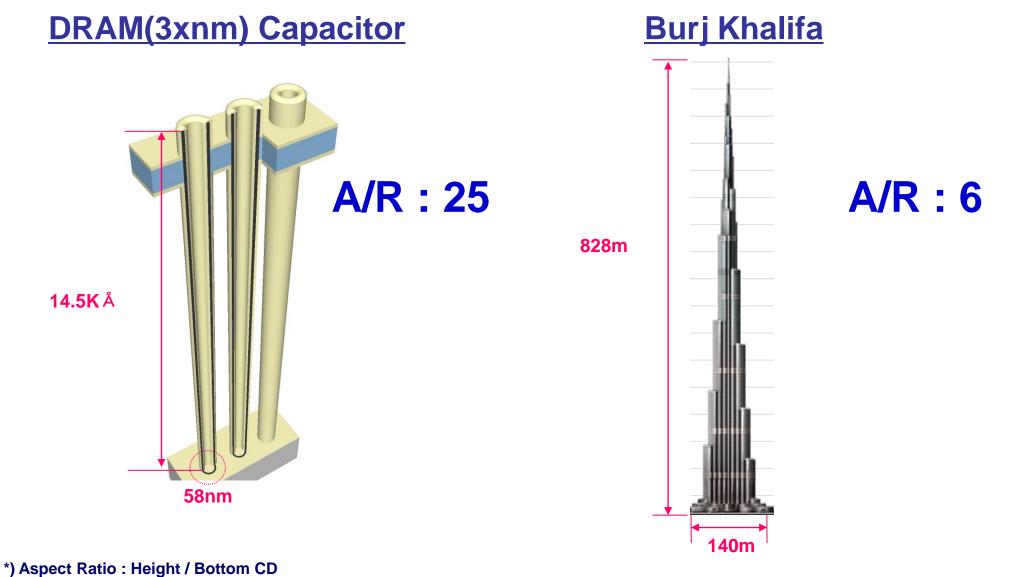

### **DRAM Challenge : Capacitor**

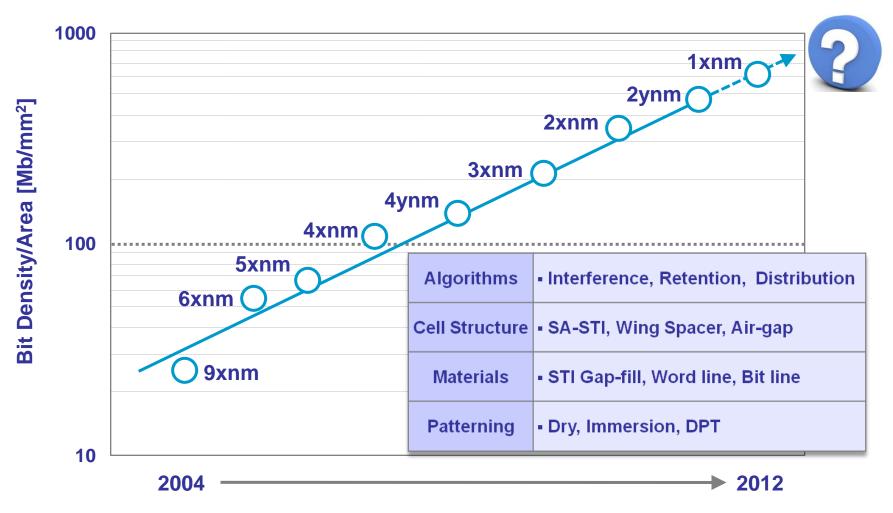

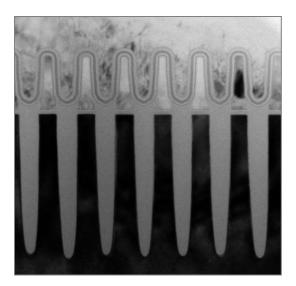

### **NAND Process Scaling : Lower Cost**

### Increase of bit density/area by ~50% per year

One Tech-node per year

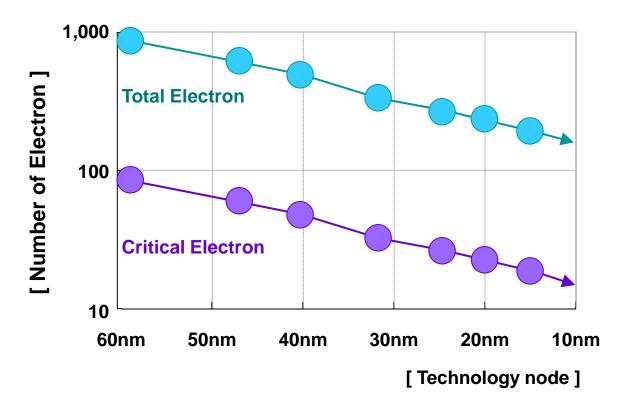

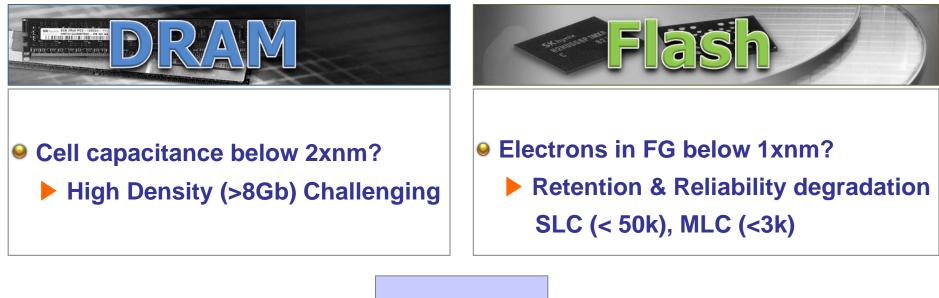

## **FG Limitation : Number of Electrons**

### How to Manage 10 electrons in sub-1xnm design rule?

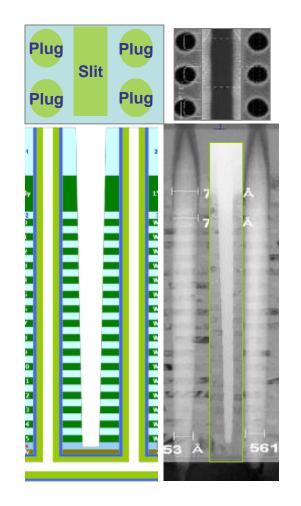

# **Key Questions in NAND Scaling**

| Issues with 10nm FG |                  | Solutions |

|---------------------|------------------|-----------|

| X - direction       | CG poly-Si void  |           |

|                     | Interference     |           |

|                     | Bit-Line loading |           |

| Y - direction       | WL bending       |           |

|                     | Interference     |           |

|                     | WL-to-WL leakage |           |

**10nm FG?**

**3D NAND?**

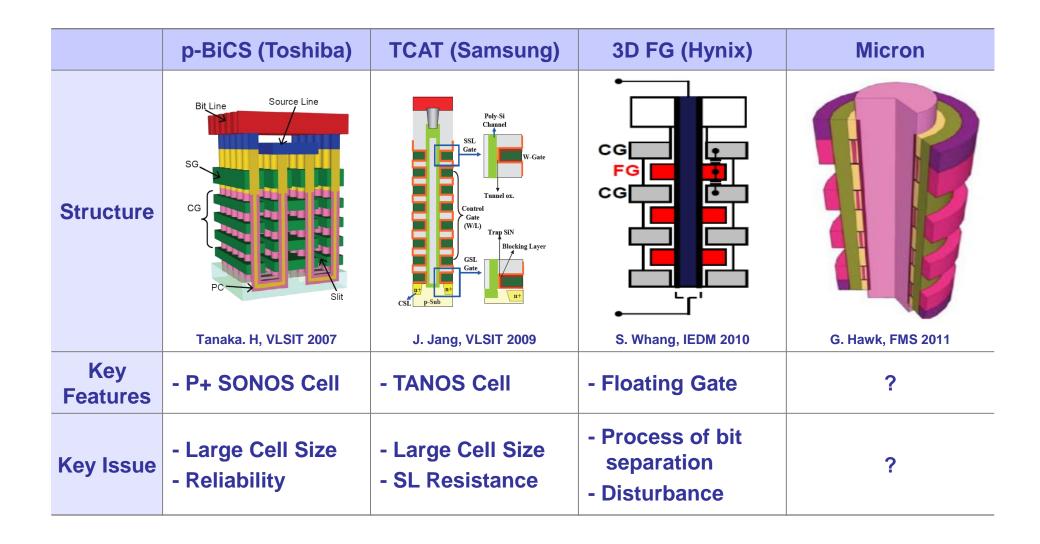

### **Proposed 3D NAND Structure**

# **3D NAND Challenges : Yield & Retention**

### Factors for Yield

- Stabilization of multi-stack patterning

- Metrology

- Defect monitoring for deep inside 3D-structure

- Poor data retention

- Needs careful cell optimization

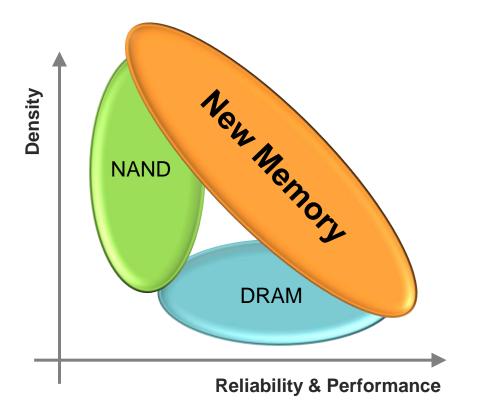

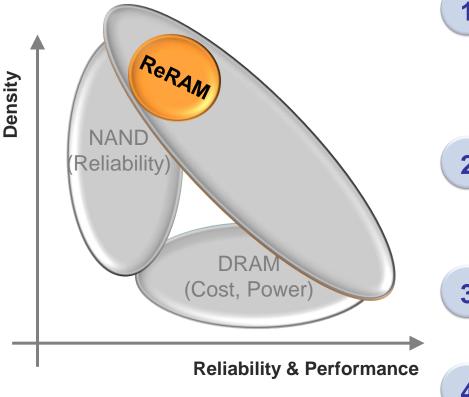

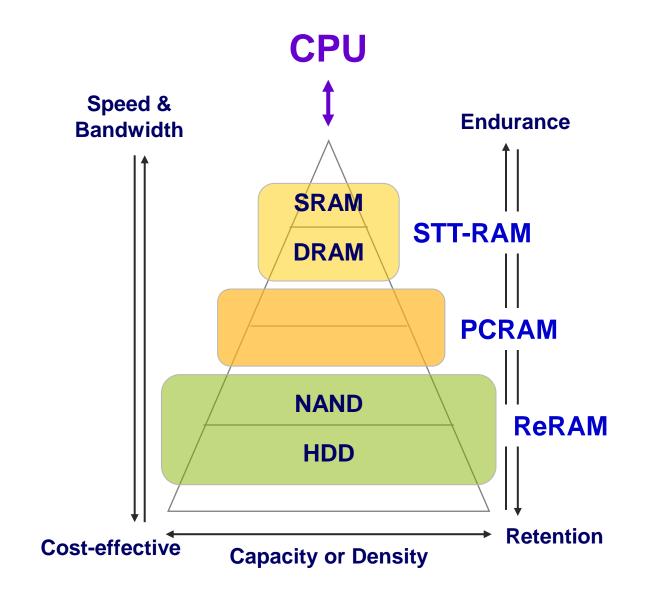

# Why New Memory?

### **Limitations of Conventional Memory Devices**

### **New Memory with Improved Scalability & Reliability**

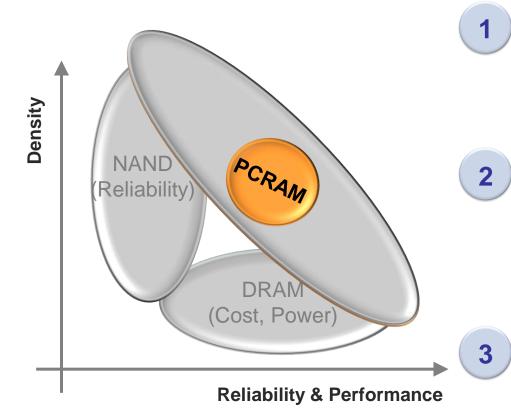

# **New Memory : Potential**

Replace existing memory

- Breakthrough on DRAM retention

- Breakthrough on NAND reliability

#### 2 Upgrade system performance

- Reduce the latency gap

- Lower power consumption

3 More scalable solution

- Lower cost

- Smaller form factor

# **New Memory : Requirements**

#### Drop in Replacement

Compatible Interface with Conventional Memory (DDRx / LPDDRx)

#### Cost & Power (vs. DRAM)

Cost Down & No Refresh-Power (Scalability & Non-Volatile)

#### Reliability & Performance (vs. NAND)

Implement Native High IOPS (Byte Operation, Better than NAND Reliability)

\*) New memory technology should meet at least one of requirements

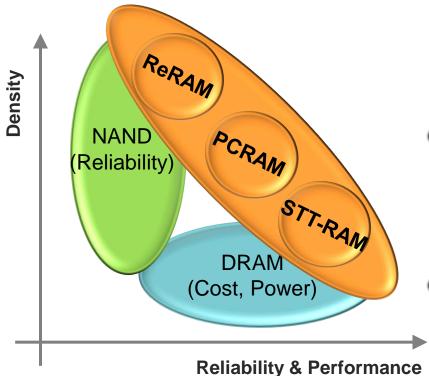

# **New Memory : High Performance**

- DRAM-like Byte Accessability

- Fast & Direct transfer between CPU and High Density Storage

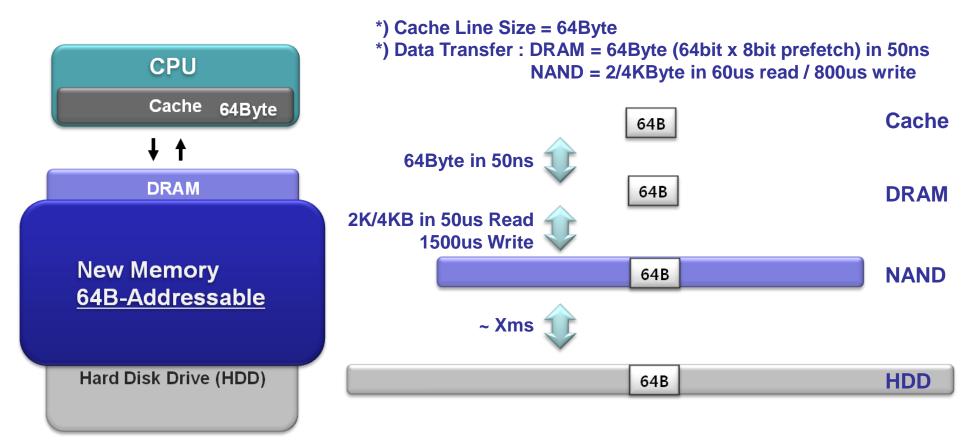

# **New Memory : Function & Position**

### **Server Blade**

1.L3 Cache Extension

► STT-RAM

2.Working Memory

► Hybrid STT-RAM & PCRAM

3. Memory Blade → PCRAM / ReRAM

4. IO Accelerator5. SSD6. HDD

► PCRAM / ReRAM

## **PCRAM : Opportunities & Concerns**

Advantages of Ge-Sb-Te

- Non-volatility / Phase change phenomena

- Good scalability (< 5nm)

Not replacing but making a new class (Upgrade the system performance)

- DRAM-like (Memory-like) : Hybrid

- NAND-like (Storage-like)

- **Concerns for DRAM-like application**

- Cost <  $1/2 \times DRAM$

- Active power : relatively large reset current

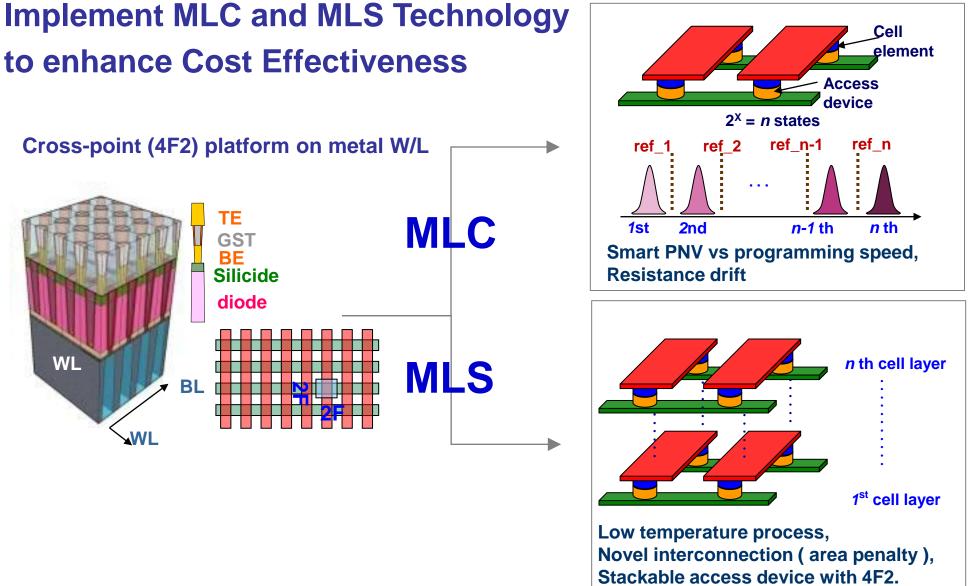

# **PCRAM : Technology Update**

Smaller heater geometry, optimization of heater & GST materials.

# **PCRAM : Technology Update (2)**

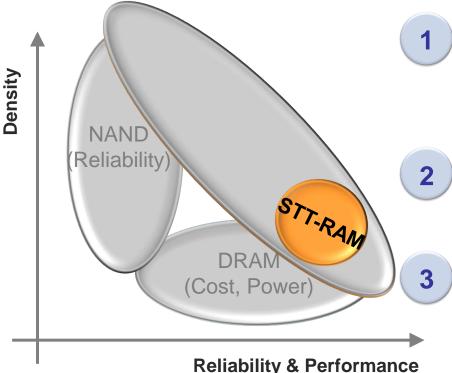

# **STT-RAM : Opportunities & Concerns**

Advantages of MTJ (Magnetic Tunnel Junction)

- Non-volatility / High speed operation

- Good scalability (PMA MTJ < 10nm)

Unique solution for next Working Memory - DRAM replacement

#### **Concerns for DRAM replacement**

- Cost competitiveness

- AC timing / Active power / Band Width

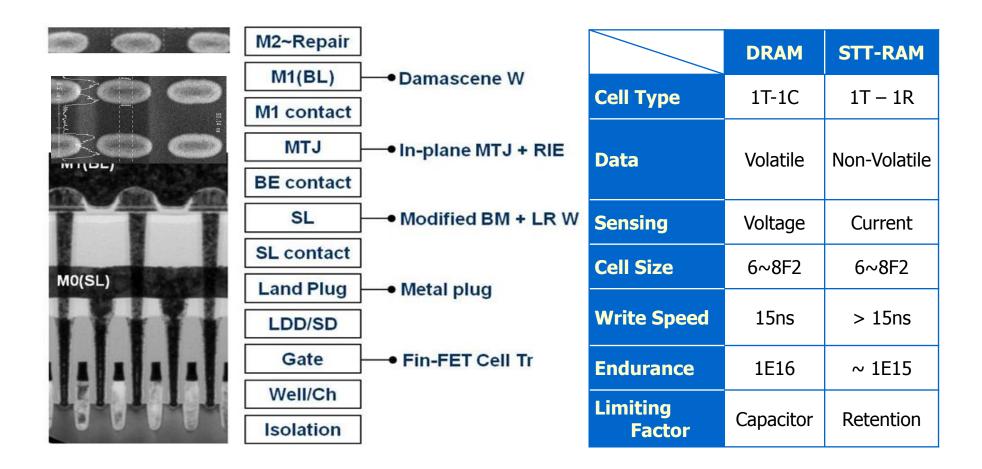

# **STT-RAM : Technology Update**

- Low MTJ switching current, High thermal stability

- : Perpendicular Magnetic Anisotropy

- Bit line Source line Gate BE TN B

- Complicated MTJ stacking structure

- : Most critical part.

### STT-RAM test chip (IEDM 2010)

•DRAM friendly cell structure and process integration.

### **Technical Challenges**

MTJ switching current → major concerning issue ( retention, distribution, read margin )

**1. MTJ patterning process without degradation of MTJ properties**

- Etching (slope, sidewall damage, shunt...)

- 2. The reduced total parasitic resistance

- High performance cell transistor (cell size 14F2 → ?F2)

- Interconnection resistance (array size limitation)

- 3. Small data signal (High/Low resistance ratio ~2.5)

- Required Large Sense amp size

- Required High TMR (>200%)

#### 4. ECC and Memory controllers

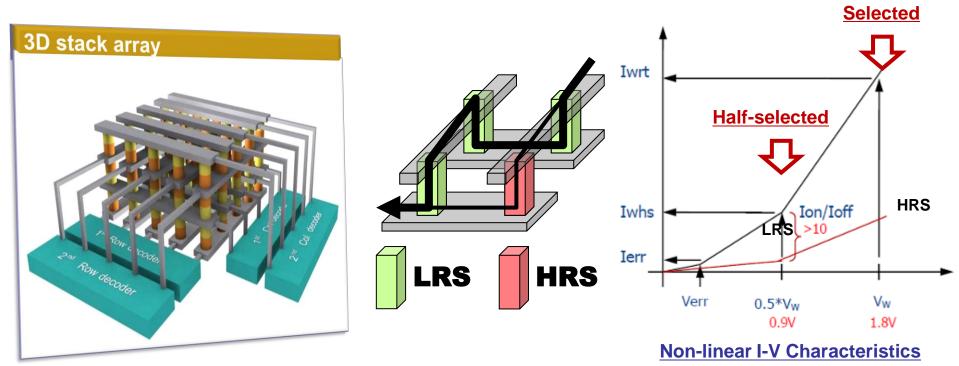

## **ReRAM : Opportunities & Concerns**

**Memristor Cell** 1 - Very simple materials & structure - Low power operation : Non-volatile, Vsw<3V, Isw <10uA High density storage capability 2 - Simple & stackable cell - NAND or HDD replacement 3 **High performance SCM capability** - Fast Access & Good Endurance **Concerns for memory application** 4 Various & unclear switching mechanism

## **ReRAM : Technology Update**

- Maximize the cell array efficiency

- Multi stack cross bar array architecture

- Small core overhead : Buried core circuits

- Memristor : Simple cell structure ( no switching device )

- Suppress sneak current : highly non-linear I-V

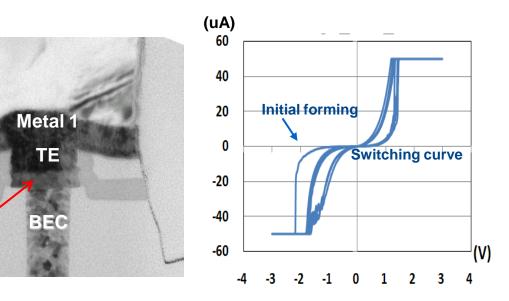

## **ReRAM : Technology Update (2)**

### Memristor cell Technology

- Simple TMO (Transition metal oxide)

- Binary switching : symmetric

- Good non-linear I-V : Kw

- Low Reset current

TMO

#### VSLI

| Items        | Sample       |

|--------------|--------------|

| I_reset (CC) | < 50uA       |

| V_sw_dc      | 1.6 V        |

| Kw           | > 10         |

| on/off       | ~ 10         |

| V_forming    | 2.0 V        |

| AC endurance | > 1e4 cycles |

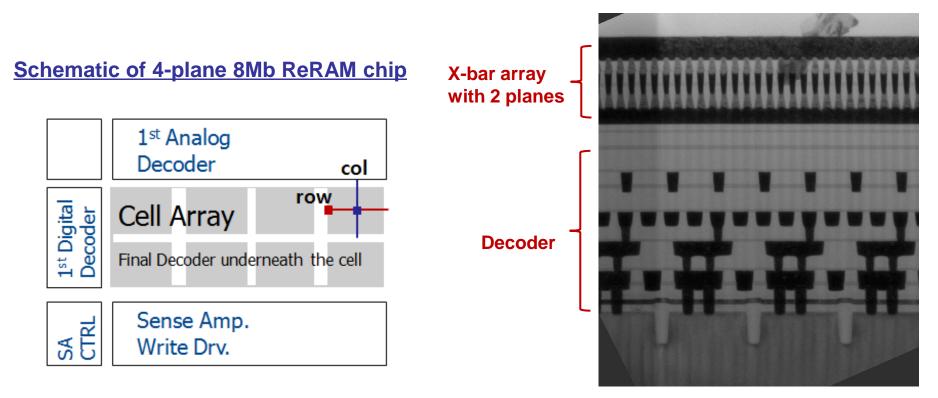

## **ReRAM : Technology Update (3)**

Multi-planes for high density & cost-efficiency

- 8Mb chip design for cross bar array with multi planes

- Decoders underneath cell array.

<sup>&</sup>lt;Source : SOVT, USA 2012>

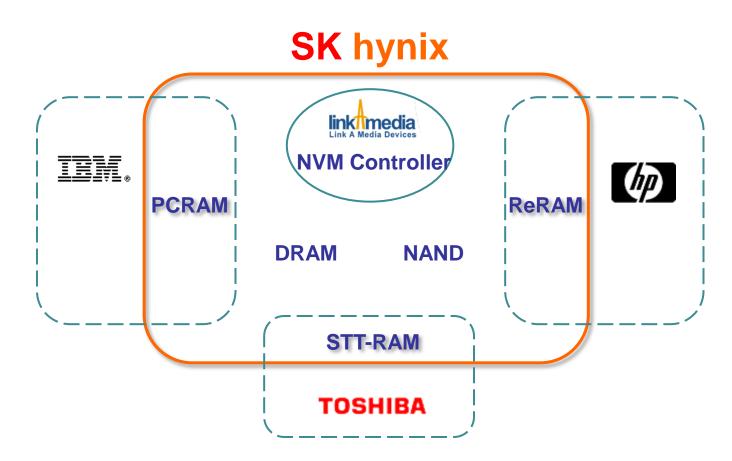

## **SK Hynix New Memory Strategy**

### **New Memory Status in SK hynix**

- Joint Development with IBM, HP, Toshiba

- Developing NVM Controller by Link A Media

### **Summary**

**Cost effectiveness of 1xnm DRAM and NAND flash ?**

Developing Three types of New Memory

- PCRAM, STT-RAM, ReRAM

Possible Position of New Memory

- PCRAM : SCM / Working Memory

- STT-RAM : Working Memory / Cache Memory

- ReRAM : Storage / SCM